# Studies on Logic Simulation and Hardware Description Languages

# Nagisa ISHIURA

December 1990

# Studies on Logic Simulation and Hardware Description Languages

# Nagisa ISHIURA

December 1990

# Studies on Logic Simulation and Hardware Description Languages

Nagisa ISHIURA

### Abstract

With the recent advances of semiconductor technologies, larger and larger and more and more sophisticated digital systems can be realized as hardware, which in turn makes it difficult to achieve design verification of hardware. In this thesis three major topics in logic design verification and hardware description languages are discussed. One is on acceleration of logic simulation speed. The increase in computation cost for logic simulation has been and will be the primary problems in design verification. As a solution to this problem, fast simulation methods utilizing vector supercomputers are proposed. Another topic is on accuracy of logic simulation. In verification of circuits which depends on subtle timing relations, trade-offs between accuracy and computation cost of simulation becomes an important issue. Discussions are created on this issue both from theoretical and practical point of view. The last topic is on hardware description languages. A new model of hardware which can be a base of formal semantics of hardware description languages is presented.

As for acceleration of logic simulation speed, fast logic simulation techniques utilizing *vector supercomputers* are proposed. Vector supercomputers are computers which have special facilities to execute operations on vectors extremely fast. In chapter 3 and chapter 4, new algorithms of logic simulation and fault simulation, respectively, are presented which efficiently bring out the potential of vector super computers.

In chapter 3, three types of simulation algorithms are proposed which are dedicated for 1) zero-delay simulation of combinational circuits, 2) zero-delay simulation of synchronous sequential circuits, and 3) simulation with delay consideration. The first two are based on the compilerdriven method. High vectorization ratio is achieved by processing many input patterns or simulating many gates at a time. Combinational use of the vectorization algorithms and the bit oriented vector logical operations makes it possible to achieve  $7.7 \times 10^9$  gate-evaluations per second for combinational circuit simulation and  $1.4 \times 10^9$  gate-evaluations per second for sequential circuit simulation on the supercomputer FACOM VP-200. The acceleration ratio through vectorization is more than 15. The third algorithm for timing simulation is an extension of the conventional event-driven simulation algorithm. Vectorization is achieved by processing all the events together which are scheduled to occur at the same time period. A simulator implemented based on the algorithm marked  $230 \times 10^3$  events per second on the supercomputer HITAC S-810/20. These performance figures are comparable to those of hardware simulation engines.

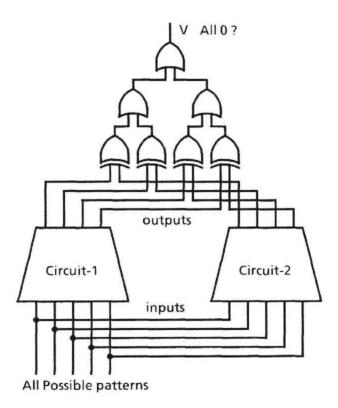

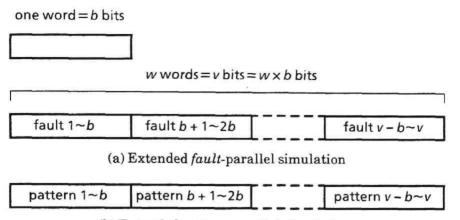

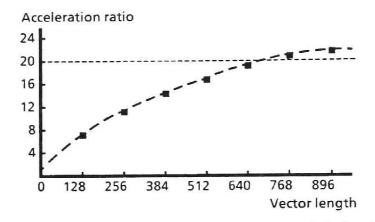

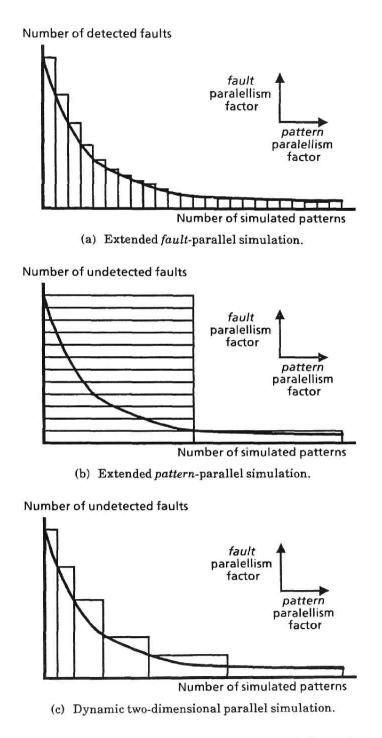

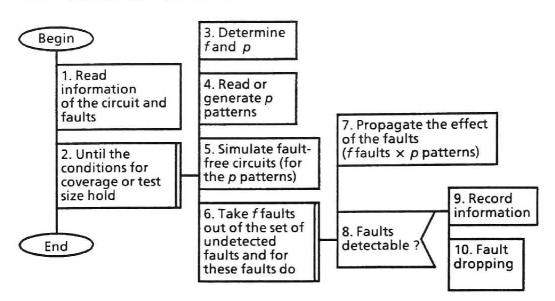

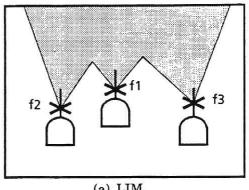

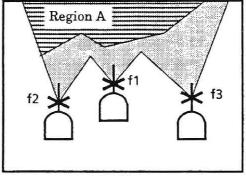

In chapter 4, a vector supercomputer oriented fault simulation algorithm, named a dynamic 2-dimensional parallel fault simulation is proposed which is dedicated for zero-delay two-valued fault simulation of gate-level combinational circuits with single stuck-at faults. The *bitparallel simulation technique* which is one of the basic algorithms of fault simulation is extended to *two-dimensional parallel simulation technique*. In this technique many faults for many patterns are processed at a time by vector bitwise logical operations. Although high vectorization ratio is achieved in this method, it does not necessarily lead to efficient fault simulation if we try to combine it with the fault dropping which is an indispensable technique for reducing the computation cost. In order to counter this problem, *dynamic adjustment* of the two parallelism factors is introduced. Experimental results on coverage estimation of random patterns are shown, in which the fault simulator implemented on the FA-COM VP-200 supercomputer achieved acceleration ratio of 15 through vectorization and succeeded in simulating 500,000 random patterns on a circuit of 3,000 gates within 30 seconds.

As alternatives to logic simulators on general purpose computers, special purpose hardware for logic simulation and fault simulation have been developed, which achieves very high performance by parallel computation scheme. However, there are trade-offs between simulation speed and flexibility, or affinity for existing CAD systems on general purpose computers. The new approach of developing logic simulators and fault simulators on general purpose vector supercomputer is expected to be the one that fills the gap between software solutions on conventional scalar computers and hardware solutions.

As for accuracy of logic simulation, discussions are created focusing on a delay model under which delay values are not definite and are specified with their minimum and maximum values. At first the difficulty of logic simulation problem under the delay model is theoretically clarified, and then efficient algorithms to solve the problems are proposed.

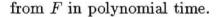

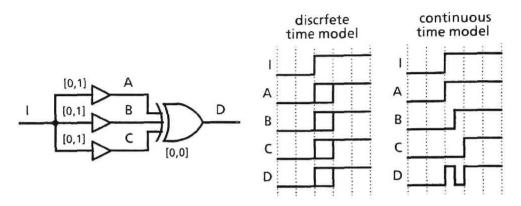

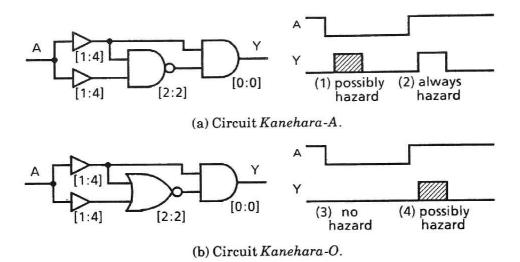

Chapter 5 is dedicated for the theoretical consideration on modeling of delay and computational difficulty of a *hazard detection problem*. Relation among models of delay and time, accuracy of verification results and computation cost for the verification is discussed taking the hazard detection problem as an example. We also discuss the difference of a discrete time model and a continuous time model. It is shown that the problem of detecting hazards on combinational circuits under uncertain delay assumption is computationally intractable (NP-hard) and that it is hence difficult to solve the problem by a simple extension of the min/max delay simulation technique. It is also shown that there is an essential difference in the verification results obtained based on the discrete time model and the continuous time model. The verification result can be more optimistic in the discrete time model than in the continuous time model. Further discussions are created on the relation between the continuous time model and the discrete time model, in which a lower bound of the width between ticks that make the discrete time model equivalent to the continuous time model.

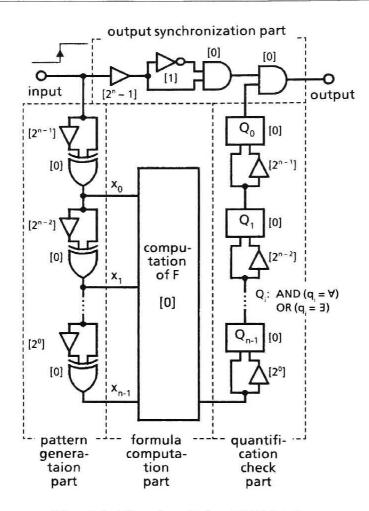

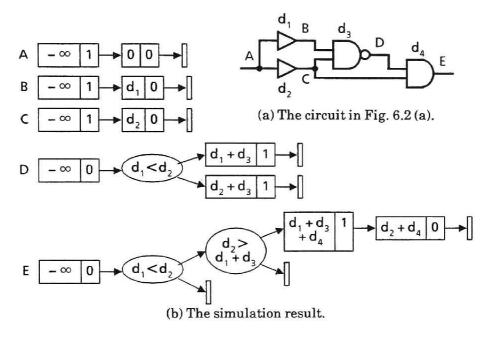

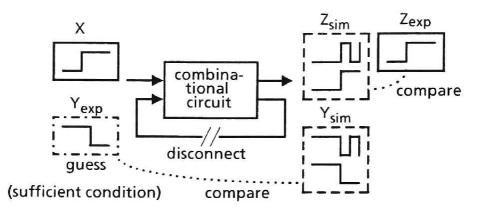

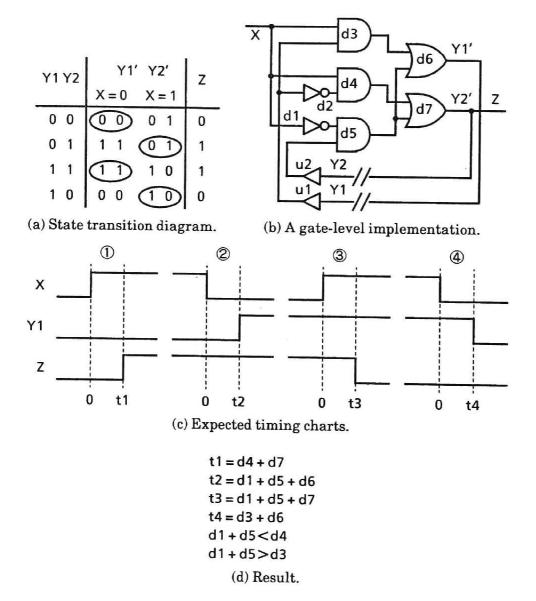

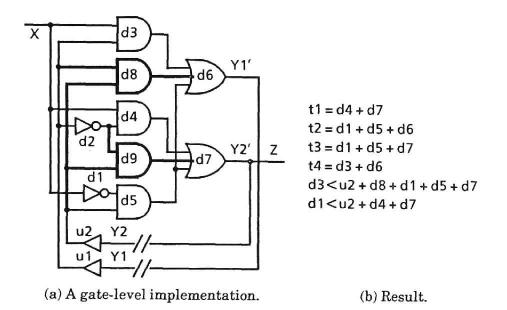

In chapter 6, a new simulation technique named time-symbolic simulation is presented which enables accurate simulation under the uncertainty delay model. The conventional min/max delay simulation techniques have been suffering from pessimistic results brought about by reconvergent fanouts. In time-symbolic simulation the uncertain delay value is expressed by a variable, which makes it possible to avoid the pessimism at reconvergent gates. Time-symbolic simulation also enables us to get conditions where the circuit under test behaves as expected, which is of good use for error analysis and for design improvements.

It is difficult to adapt conventional simulation algorithms to timesymbolic simulation. In this chapter, two efficient simulation algorithms for time-symbolic simulation are proposed. One is dedicated for combinational circuits and processes the algebraic formulas representing time by means of the *linear programming*. The other algorithm, which is named *coded time-symbolic simulation (CTSS)*, can handle any kind of gate-level logic circuits. In the CTSS an uncertain delay value is represented using a set of Boolean variables based on binary coding which encodes all the cases of delay values. Simulation is executed by means of *Boolean* function manipulation. Both of the simulators are shown to run within a feasible time for small scale circuits up to 100 gates. In this chapter, various techniques are also proposed for verification of asynchronous circuits based on time-symbolic simulation and for analysis of simulation results.

The importance of the symbolic approach in this chapter lies in that we

#### Abstract

can analyze the simulation result so as to get useful information on error correction and design improvements, as well as in that we can get accurate simulation results. Symbolic simulation, including time-symbolic and value-symbolic approaches, will be one of the most important techniques for logic design verification along with conventional logic simulation.

The last part of this thesis is dedicated for the discussion on formal semantics of hardware description languages. In the trend of standardization, definition of formal semantics of practical hardware description languages is an important issue. In order to define formal semantics of hardware description languages which can support various applications such as logic synthesis and formal verification as well as logic simulation, a model of hardware is indispensable which can express uncertain behavior of hardware in a strict since. In this thesis, a new behavior model of hardware named NES (Nondeterministic Event Sequence) is proposed. The NES can express the uncertainty of hardware behavior by means of nondeterminism. The behavior of hardware is modeled by nondeterministic abstract machines and is dealt with as a set of all the possible behaviors. In chapter 7, the formal definition of the NES model, and a modeling method of a hardware module and connected hardware modules are presented. Also as an application of the NES model, definition of the semantics of a hardware description language UDL/I is described.

The applications of hardware description languages will be wider and wider. The nondeterministic semantics, which plays an indispensable role in expressing the relations between behavior of circuits in different design levels, is considered to be an essential factor of hardware description languages of the next generation, which can be a basis of variety of applications such as logic synthesis, formal verification, symbolic simulation, and so on.

# Contents

| Ał | ostra | ct      |                                                  | i         |

|----|-------|---------|--------------------------------------------------|-----------|

| Co | onten | its     |                                                  | vii       |

| 1  | Intr  | oducti  | on                                               | 1         |

|    | 1.1   | Backgr  | rounds                                           | 1         |

|    | 1.2   | Outlin  | e of the Thesis                                  | 5         |

| 2  | Logi  | ic Sim  | ulation                                          | 11        |

|    | 2.1   | Modeli  | ing of Logic Circuits for Logic Simulation       | 11        |

|    |       | 2.1.1   | Modeling of Structure of Logic Circuits          | 11        |

|    |       | 2.1.2   | Modeling of Signal Values                        | 11        |

|    |       | 2.1.3   | Modeling of Time                                 | 14        |

|    |       | 2.1.4   | Modeling of Delay                                | 14        |

|    |       | 2.1.5   | Logic Simulation                                 | 16        |

|    | 2.2   | Basic . | Algorithms for Logic Simulation                  | 17        |

|    |       | 2.2.1   | Compiler-Driven Simulation and Event-Driven Sim- |           |

|    |       |         | ulation                                          | 17        |

|    |       | 2.2.2   | S-Algorithm and T-Algorithm                      | 18        |

|    |       | 2.2.3   | Code Generation Method and Table-Driven Method   | 21        |

|    |       | 2.2.4   | Ordering of Gate Evaluations                     | 22        |

| 3  | Fast  | Logic   | Simulation Using Vector Super Computers          | <b>25</b> |

|    | 3.1   | Introd  | uction                                           | 25        |

|   | 3.2  | Vector                                                  | Supercomputers                                     | 28 |  |  |  |  |  |

|---|------|---------------------------------------------------------|----------------------------------------------------|----|--|--|--|--|--|

|   | 3.3  | Vector                                                  | ization of Combinational Circuit Simulation        | 32 |  |  |  |  |  |

|   |      | 3.3.1                                                   | Vector-Parallel Simulation Technique               | 32 |  |  |  |  |  |

|   |      | 3.3.2                                                   | Reduction of Storage Requirements Based on DF-     |    |  |  |  |  |  |

|   |      |                                                         | Sorting                                            | 33 |  |  |  |  |  |

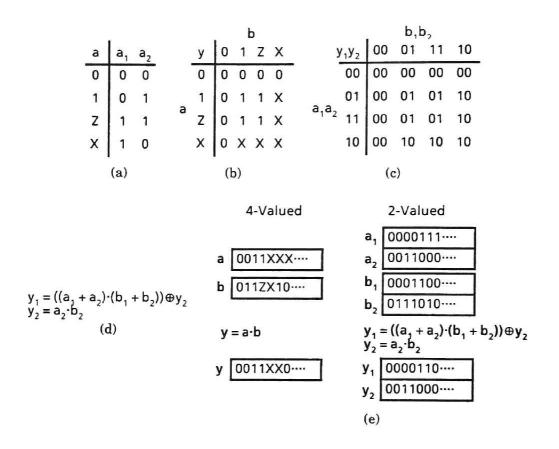

|   |      | 3.3.3                                                   | Multi-Valued Logic Simulation                      | 37 |  |  |  |  |  |

|   |      | 3.3.4                                                   | Implementation and Experiments                     | 42 |  |  |  |  |  |

|   |      | 3.3.5                                                   | Considerations for Further Acceleration            | 48 |  |  |  |  |  |

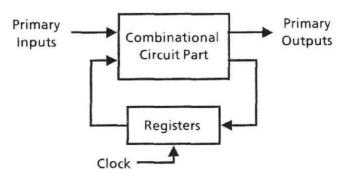

|   | 3.4  | Vector                                                  | ization of Sequential Circuit Simulation           | 48 |  |  |  |  |  |

|   |      | 3.4.1                                                   | Gate Grouping Technique                            | 48 |  |  |  |  |  |

|   |      | 3.4.2                                                   | Grouping Algorithms Based on DF-Sorting            | 52 |  |  |  |  |  |

|   |      | 3.4.3                                                   | Implementation and Performance Evaluation          | 55 |  |  |  |  |  |

|   |      | 3.4.4                                                   | Code-Generation Method vs. Table-Driven Method     | 59 |  |  |  |  |  |

|   |      | 3.4.5                                                   | Modeling of Circuits                               | 60 |  |  |  |  |  |

|   | 3.5  | Vector                                                  | ization of Event-Driven Simulation                 | 60 |  |  |  |  |  |

|   |      | 3.5.1                                                   | Vectorization of Event Processing                  | 60 |  |  |  |  |  |

|   |      | 3.5.2                                                   | Event Fetch                                        | 62 |  |  |  |  |  |

|   |      | 3.5.3                                                   | Event Propagation                                  | 64 |  |  |  |  |  |

|   |      | 3.5.4                                                   | Gate Evaluation                                    | 66 |  |  |  |  |  |

|   |      | 3.5.5                                                   | Event Registration                                 | 68 |  |  |  |  |  |

|   |      | 3.5.6                                                   | Implementation and Performance Evaluation $\ldots$ | 70 |  |  |  |  |  |

|   |      | 3.5.7 Compiler-Driven Method vs. Event-Driven Metho     |                                                    |    |  |  |  |  |  |

|   | 3.6  | Remai                                                   | rks and Discussions                                | 72 |  |  |  |  |  |

| 4 | Fast | t Fault                                                 | Simulation Using Vector Super Computers            | 75 |  |  |  |  |  |

|   | 4.1  | Introd                                                  | uction                                             | 75 |  |  |  |  |  |

|   | 4.2  | 2 Dynamic Two-Dimensional Parallel Simulation Technique |                                                    |    |  |  |  |  |  |

|   |      | 4.2.1                                                   | Fault Simulation                                   | 77 |  |  |  |  |  |

|   |      | 4.2.2                                                   | Two-Dimensional Parallel Simulation                | 79 |  |  |  |  |  |

|   |      | 4.2.3                                                   | Dynamic Adjustment of the Parallelism Factors      | 81 |  |  |  |  |  |

|   | 4.3 | Multipl | le Fault Propagation                                                                                              | 84  |

|---|-----|---------|-------------------------------------------------------------------------------------------------------------------|-----|

|   |     | 4.3.1   | Selective Tracing                                                                                                 | 84  |

|   |     | 4.3.2   | Implementation of Selective Tracing                                                                               | 85  |

|   |     | 4.3.3   | Determination of Parallelism Factors                                                                              | 91  |

|   | 4.4 | Implem  | nentation and Experiments                                                                                         | 93  |

|   |     | 4.4.1   | Simulation Speed                                                                                                  | 93  |

|   |     | 4.4.2   | Required Storage Size                                                                                             | 96  |

|   | 4.5 | Remar   | ks and Discussions                                                                                                | 96  |

| 5 | Cor | nputati | ional Complexity of Logic Simulation Problems                                                                     | 99  |

|   | 5.1 | Introdu | $uction \ldots \ldots$ | 99  |

|   | 5.2 | Hazard  | d Detection Problem and Modeling of Delay and Time                                                                | 101 |

|   |     | 5.2.1   | Hazard Detection Problem                                                                                          | 101 |

|   |     | 5.2.2   | Modeling of Delay and Time                                                                                        | 102 |

|   |     | 5.2.3   | Notation                                                                                                          | 104 |

|   | 5.3 | Hazard  | $1$ Detection Problems of the Discrete Time Model $\ .$                                                           | 105 |

|   | 5.4 | Relatio | on between the Continuous Time Model and the Dis-                                                                 |     |

|   |     | crete 7 | Time Model                                                                                                        | 108 |

|   |     | 5.4.1   | Difference between the Continuous Time Model and                                                                  |     |

|   |     |         | the Discrete Time Model                                                                                           | 108 |

|   |     | 5.4.2   | The Linear Inequality System Equivalent to a Haz-                                                                 |     |

|   |     |         | ard Detection Problem                                                                                             | 111 |

|   |     | 5.4.3   | Reduction of Continuous Time Model into Discrete                                                                  |     |

|   |     |         | Time Model                                                                                                        |     |

|   | 5.5 | Hazaro  | d Detection Problems of the Continuous Time Model                                                                 |     |

|   |     | 5.5.1   | Exponential Delay and Discrete Time Model                                                                         | 115 |

|   |     | 5.5.2   | An Upper Bound of the Computational Complex-                                                                      |     |

|   |     |         | ity of Hazard Detection Problem of the Continuous                                                                 |     |

|   |     |         | Time Model                                                                                                        |     |

|   | 5.6 | Remar   | ks and Discussions                                                                                                | 120 |

| 522 B B    |

|------------|

| Contents   |

| Conteentee |

|            |

|   | 5.A  | Proof o | of Lem 5.5                                          | 122  |

|---|------|---------|-----------------------------------------------------|------|

| 6 | Tim  | e-Sym   | bolic Simulation for Accurate Timing Verifica       | -    |

|   | tion |         |                                                     | 125  |

|   | 6.1  | Introdu | 1ction                                              | 125  |

|   | 6.2  | Problem | ms of Conventional Min/Max Delay Simulation         | 128  |

|   | 6.3  | Time-S  | Symbolic Simulation Based on T-Algorithm            | 130  |

|   |      | 6.3.1   | Modeling of Uncertain Delay Using Time Variables    | 130  |

|   |      | 6.3.2   | Algorithm Based on S-Algorithm                      | 131  |

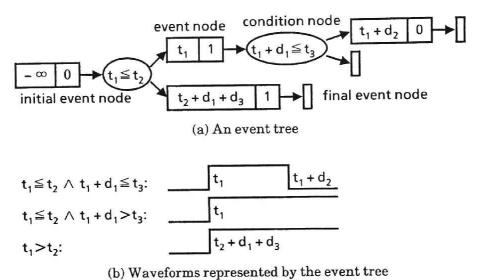

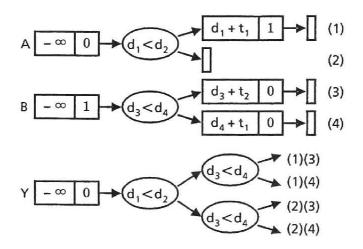

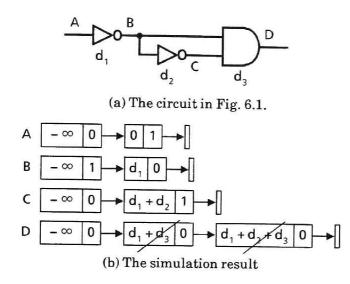

|   |      | 6.3.3   | Representation of a Signal History by an Event Tree | e132 |

|   |      | 6.3.4   | Algorithm of Gate Evaluation                        | 133  |

|   |      | 6.3.5   | Manipulation of Algebraic Expressions               | 138  |

|   | 6.4  | Timing  | g Verification by Time-Symbolic Simulation          | 138  |

|   |      | 6.4.1   | Hazard Detection                                    | 138  |

|   |      | 6.4.2   | Verification of Asynchronous Sequential Circuits .  | 139  |

|   |      | 6.4.3   | Result-Analysis System                              | 143  |

|   |      | 6.4.4   | Performance of the Simulator                        | 144  |

|   | 6.5  | Coded   | Time-Symbolic Simulation - CTSS                     | 144  |

|   |      | 6.5.1   | Modeling of Uncertain Delay by Boolean Variables    | 145  |

|   |      | 6.5.2   | Representation of Boolean Functions by a Shared     |      |

|   |      |         | Binary Decision Diagram                             | 147  |

|   | 6.6  | Timing  | g Verification by Coded Time-Symbolic Simulation .  | 151  |

|   |      | 6.6.1   | Result Analysis of the CTSS                         | 151  |

|   |      | 6.6.2   | Analysis of Simulation Results Based on Symbolic    |      |

|   |      |         | Simulation of Finite Automata                       | 151  |

|   |      | 6.6.3   | Extraction of Algebraic Expressions                 | 153  |

|   |      | 6.6.4   | Implementation Issues                               | 153  |

|   |      | 6.6.5   | Experimental Results                                | 155  |

|   | 6.7  | Reman   | cks and Discussions                                 | 156  |

x

| 7                  | NES               | 5: A N                                         | ondeterministic Behavior Model for Hardwar                                                          | e    |  |  |  |  |  |

|--------------------|-------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|--|--|--|--|--|

|                    | Des               | criptio                                        | n Languages                                                                                         | 159  |  |  |  |  |  |

|                    | 7.1               | Introd                                         | uction                                                                                              | 159  |  |  |  |  |  |

|                    | 7.2               | Basic                                          | Concepts of the NES Model                                                                           | 162  |  |  |  |  |  |

|                    |                   | 7.2.1                                          | Modeling of Uncertainty by Nondeterminism                                                           | 162  |  |  |  |  |  |

|                    |                   | 7.2.2                                          | Modeling of a Zero Delay                                                                            | 164  |  |  |  |  |  |

|                    | 7.3               | Model                                          | ing and Description of Behavior of a Hardware Modul                                                 | e165 |  |  |  |  |  |

|                    |                   | 7.3.1                                          | Modeling of Waveforms                                                                               | 165  |  |  |  |  |  |

|                    |                   | 7.3.2                                          | Modeling of Behavior of a Module                                                                    | 167  |  |  |  |  |  |

|                    |                   | 7.3.3                                          | Description of Behavior of Modules                                                                  | 168  |  |  |  |  |  |

|                    |                   | 7.3.4 Description of a Zero-Delay Unit         |                                                                                                     |      |  |  |  |  |  |

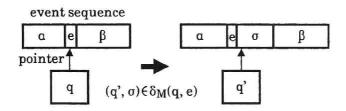

|                    |                   | 7.3.5                                          | Simulation of the Abstract Machine                                                                  | 171  |  |  |  |  |  |

|                    | 7.4               | Modeling and Descriptions of Connected Modules |                                                                                                     |      |  |  |  |  |  |

|                    |                   | 7.4.1                                          | Modeling of Connected Modules                                                                       | 172  |  |  |  |  |  |

|                    |                   | 7.4.2                                          | Description of Connected Modules                                                                    | 174  |  |  |  |  |  |

|                    | 7.5               | Applie                                         | cations of the NES Model                                                                            | 175  |  |  |  |  |  |

|                    |                   | 7.5.1                                          | Definition of Semantics of UDL/I                                                                    | 175  |  |  |  |  |  |

|                    |                   | 7.5.2                                          | Nondeterministic Semantics and CAD Tools                                                            | 177  |  |  |  |  |  |

|                    | 7.6               | Rema                                           | rks and Considerations                                                                              | 178  |  |  |  |  |  |

| 8                  | Cor               | ıclusio                                        | ns                                                                                                  | 181  |  |  |  |  |  |

| R                  | References        |                                                |                                                                                                     |      |  |  |  |  |  |

| Acknowledgment 197 |                   |                                                |                                                                                                     |      |  |  |  |  |  |

| Li                 | st of             | Publi                                          | cations by the Author                                                                               | 199  |  |  |  |  |  |

|                    | Maj               | or Publ                                        | lications $\ldots$ | 199  |  |  |  |  |  |

|                    | Technical Reports |                                                |                                                                                                     |      |  |  |  |  |  |

# Chapter 1

# Introduction

# 1.1 Backgrounds

Recent advances of semiconductor technologies have made it possible to realize large and sophisticated hardware as integrated circuits, which have brought digital systems to wide variety of applications. On the other hand, the size and the complexity of the hardware have made the design processes more and more difficult. It is almost impossible to design hardware of required scale and complexity without the help of *computeraided design (CAD)* systems.

Among many steps of designing hardware, *design verification* is one of the most laborious ones. The most effective and the most widely used means of verifying correctness of design is *logic simulation*, that is to simulate the behavior of circuit under test on computers.

Computation time required for logic simulation is roughly proportional to the size of a circuit under test and to the length of test pattern sequence. The increase in circuit size, together with the incidental increase in test pattern size, has resulted in rapid growth of the computation time for the simulation. It is reported that about 1800 hours of IBM 370/168 CPU time were required to verify the logic design of 1/4 of a mediumrange System 370 CPU [Den83]. It is one of the most important subject in the area of CAD of digital systems to develop high-speed logic simulation techniques. A number of research efforts have been carried out in recent years in order to reduce computation time for logic simulation, which include improvements in modeling of logic circuits, development of efficient simulation algorithms [Bre76, Ulr83, Ish84], improvements in techniques in coding level [Ulr80b, Kro81], and development of special purpose hardware (hardware simulation engines) [Den83, Sas83, Bla84, Nak86, Hir87, Nag86]. Among them the special purpose hardware approach has become a center of attention because of the high performance achieved by parallel computation schemes. However, the performance is obtained at the sacrifice of flexibility and affinity for existing CAD systems on general purpose computers. It is pointed out that it often takes much longer time to compile and to transmit data than to execute simulation on hardware simulation engines. High cost by reason of special purpose hardware is also a demerit of the hardware simulation engines. On the other hand, software simulators on general purpose computers are still attractive for their latest device technologies, economical merits and flexibility. General purpose supercomputers and parallel computers can be new solutions that fill the gap between the two approaches.

Along with the computation time for logic simulation, that of *fault* simulation is another big problem in the field of CAD of digital circuits. Fault simulation is in a way a variation of logic simulation, although it is used for different purposes from logic simulation. While a logic simulator computes behavior of fault-free logic circuits, a fault simulator computes behavior of logic circuits which have faults in them. It is used for analysis of the behavior of faulty circuits, test set generation or quality evaluation of test sets for logic circuits. Fault simulation requires much more computation cost than logic simulation, because simulation must be carried out for each of the faults derived from a certain fault model. Under the single stuck-at fault assumption, the computation time in the worst case is proportional to the square of circuit size [Har87]. Various research projects have been carried out in order to accelerate fault simulation by improving algorithms [Arm72, Ulr80a, Wai85, Nis85, Ant87], or to develop alternative techniques to fault simulation [Abr83, Jai84, Brg85]. In spite of these efforts, there are still pressing requirements for faster fault simulation.

The large computation cost due to the large circuit size has been and will be one of the primary problems in design verification. On the other hand, accuracy of simulation is also an important issue. Especially in design verification of asynchronous circuits which operate based on subtle timing relations, much more laborious modeling of delay and time and also much more computation cost are required than in that of synchronous circuits. In the verification concerned with timing there are close relations among models of delay and time, accuracy of verification results and required computation cost. In a simple modeling which require smaller computation cost, design errors may be overlooked or possibilities of design errors may be indicated even for correct designs. One example is the handling of delay whose actual value is unknown and is specified with minimum and maximum values. In logic simulation the min/max delay model is employed to handle such uncertainty. The model allows relatively fast verification but it is well known that the verification results are often too pessimistic due to reconvergent fanouts [Bre76]. It has, therefore, come to be an important research theme to find efficient methods to overcome this problem [Yon89, Cer89]. Although there are many attempts to solve the problems, few discussions have been made on what is the essence of the difficulty and how difficult or how much computation cost is required to solve the problem completely. Another important issue is modeling of time. Many of the existing verification systems are based on a discrete time model [Cer89, Hir89, Nak87, Kim88]. There are also few discussions on the point if the discrete time model provides accurate result as compared with a *continuous time model* or if there is a difference in the computation cost of the verification between the two models. In order to develop efficient and yet reliable verification system, it is considered to be important to clarify the theoretical backgrounds on modeling and accuracy of verification.

Modeling and accuracy of verification are also one of the central issues in the field of hardware description languages (HDL's). Hardware description languages are kernels of CAD systems for integrated circuits which work as inputs to various CAD tools, design documents and vehicles for design interchange among different CAD systems. Although a lot of research projects have been carried out on hardware description languages, we are now confronted with a big turning point due to two trends; standardization and extension of the applications of HDL's.

Standardization of a hardware description language (HDL) has an inestimable impact on the development of hardware design, including CAD tool development and design education. There are several activities for standardization in the U.S., Europe, and Japan [Kar89, Pil83, Coe89, Har86]. Since a standard HDL is used by many users, including IC manufactures and tool developers working in various kinds of design culture, we should provide them with a method of sharing a detailed idea on the HDL. It is therefore essential to define rigid syntax and semantics of the language. Although almost all the HDL's are designed on the basis of the formal definition of syntax by a meta language like BNF, there are very few HDL's, especially among the practical ones, which has clear definition of semantics. Although there have been a lot of researches on definition of formal semantics in the area of programming languages [Bjo78]. There have been, however, few studies in the area of HDL's other than [Pil83]. Especially there have been no established models which explain the behavior of the hardware described in HDL's. In view of the trend of standardization, it is considered to be an urgent research theme to develop good behavior models for HDL's and to establish formal

methods for defining semantics of HDL's.

Extension of the applications of HDL's is also changing the situation. For many years logic simulation has been the most important application of HDL's. In practical situations semantics of an HDL is defined by means of the simulator for the HDL. However, recent researches in the area of CAD for integrated circuits have brought about outstanding development of techniques for various design support by computers. Especially logic synthesis and formal verification come to become a practical technique and there are strong demands for HDL's to support these applications. However, the simulation based semantics often causes inconsistencies in handling don't cares and uncertain behavior of hardware. In logic synthesis and formal verification, we assume all the possibilities for don't cares and uncertain hardware specifications. On the other hand, in logic simulation, they are dealt with using unknown values. This is inevitable if we consider efficiency of simulation execution but it often brings about unnatural results. It is considered to be an essential challenge to develop a formal model which can explain the don't cares and uncertain behavior of hardware in order to design hardware description languages of the next generation which are provided with rigid semantics and can be basis of various CAD applications.

## 1.2 Outline of the Thesis

In this thesis three major topics in logic design verification and hardware description languages are discussed; acceleration of logic simulation speed, accuracy of timing verification, and modeling of hardware behavior for formal semantics of hardware description languages.

### (1) Algorithms for high-speed logic simulation

As a new approach to accelerating execution speed of logic simulation, a use of *vector supercomputers* are proposed. Vector supercomputers are the computers that have special facilities to execute operations on vectors extremely fast. As is discussed in 1.1, there are trade-offs between speed performance and flexibility of high-end simulators. Logic and fault simulators on supercomputers are considered to be new a solution that fall between hardware logic simulators and software simulators on general purpose computers. In order to bring out the performance of vector supercomputers, vector processor oriented algorithms for logic and fault simulation are proposed in chapter 3 and chapter 4, respectively.

In chapter 3, three types of simulation algorithms are proposed which are dedicated for 1) zero-delay simulation of combinational circuits, 2) zero-delay simulation of synchronous sequential circuits, and 3) simulation with delay consideration. The first two are based on the compilerdriven method. High vectorization ratio is achieved by simulating many input patterns or processing many gates at a time. Combinational use of the vectorization algorithms and the bit oriented vector logical operations made it possible to achieve  $7.7 \times 10^9$  gate-evaluations per second for combinational circuit simulation and  $1.4 \times 10^9$  gate-evaluations per second for sequential circuit simulation on the supercomputer FACOM VP-200, which are faster by a factor of more than 15 as compared with conventional scalar processors. The third algorithm for timing simulation is an extension of the conventional event-driven simulation algorithm. Vectorization is achieved by processing all the events together which are scheduled to occur at the same time period. A simulator implemented based on the algorithm marked  $230 \times 10^3$  events per second on the supercomputer HITAC S-810/20. These performance figures are comparable to those of hardware simulation engines.

In chapter 4, a vector supercomputer oriented fault simulation algo-

rithm, named dynamic 2-dimensional parallel fault simulation is proposed which is dedicated for the zero-delay two-valued fault simulation of gatelevel combinational circuits with single stuck-at faults. The *bit-parallel* simulation technique which is one of the basic algorithms of fault simulation is extended to two-dimensional parallel simulation technique, in which many faults for many patterns are processed at a time by vector bitwise logical operations. Although high vectorization ratio is achieved in this method, it does not necessarily lead to efficient fault simulation if we try to combine it with the fault dropping which is an indispensable technique for reducing the computation cost. In order to counter this problem, dynamic adjustment of the two parallelism factors is combined with the two-dimensional parallel simulation technique. Experimental results on coverage estimation of random patterns are shown, in which the fault simulator implemented on the FACOM VP-200 supercomputer achieved acceleration ratio of 15 through vectorization and succeeded in simulating 500,000 random patterns on a circuit of 3,000 gates within 30 seconds.

### (2) Accuracy of logic simulation

Accuracy of logic simulation is discussed both from theoretical and practical point of view, focusing on a delay model in which actual delay values are not definite and are specified with their minimum and maximum values. At first the difficulty of the problems is theoretically clarified, and then efficient algorithms to solve the problems are proposed.

Chapter 5 is dedicated for the theoretical consideration on modeling of delay and computational difficulty of a *hazard detection problem*. Relation among models of delay and time, accuracy of verification results and computation cost for the verification is discussed taking the hazard detection problem as an example. We also discuss the difference of a discrete time model and a continuous time model. It is shown that the problem of detecting hazards on combinational circuits under uncertain delay assumption is computationally intractable (NP-hard) and that it is hence difficult to solve the problem by a simple extension of the min/max delay simulation technique. It is also shown that there is an essential difference in the verification results obtained based on the discrete time model and the continuous time model. The verification result can be more optimistic in the discrete time model than in the continuous time model. Further discussions are created on the relation between the continuous time model and the discrete time model, in which a lower bound of the width between ticks that make the discrete time model equivalent to the continuous time model.

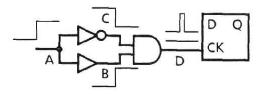

In chapter 6, a new simulation technique named *time-symbolic simulation* is presented which enables accurate simulation under the uncertainty delay model. In time-symbolic simulation the uncertain delay value is expressed by a *variable*, which makes it possible to avoid the pessimism at reconvergent gates. Time-symbolic simulation also enables us to get conditions where the circuit under test behaves as expected which is of good use for error analysis and for design improvements.

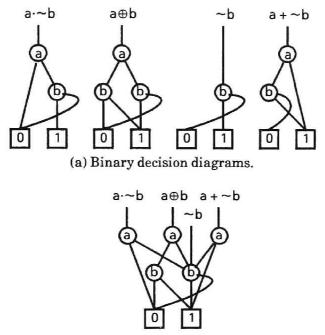

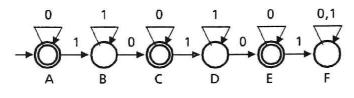

It is difficult to adapt conventional simulation algorithms for timesymbolic simulation. In this chapter, two efficient simulation algorithms for time-symbolic simulation are proposed. One is dedicated for combinational circuits and processes the algebraic formulas representing time by means of the *linear programming*. The other algorithm, which is named *coded time-symbolic simulation (CTSS)*, can handle any kind of gate-level logic circuits. In the CTSS a uncertain delay value is represented using a set of Boolean variables based on binary coding which encodes the all the cases of delay values. Simulation is executed by means of *Boolean* function manipulation. Both of the simulators are shown to run within a feasible time for small scale circuits up to 100 gates. In this chapter, various techniques are also proposed for verification of asynchronous circuits based on time-symbolic simulation and for analyzing simulation results and extracting delay conditions where the circuit under test behaves correctly.

### (3) Modeling and description of logic circuit for HDL's

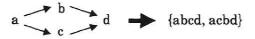

In order to define formal semantics of hardware description languages which can support various application such as logic synthesis and formal verification as well as logic simulation, a model of hardware is indispensable which can express uncertain behavior of hardware in a strict sense. In the last part of the thesis, a new behavior model of hardware named *NES* (Nondeterministic Event Sequence) is proposed. The NES can express the uncertainty of hardware behavior by means of *nondeterminism*. The behavior of hardware is modeled by nondeterministic abstract machines and we can deal the behavior of hardware as a set of all the possible behaviors.

In chapter 7, the formal definition of the NES model, and a modeling method of a hardware module and connected hardware modules are presented. Also as an application of the NES model, definition of the semantics of a hardware description language UDL/I is described.

# Chapter 2

# Logic Simulation

### 2.1 Modeling of Logic Circuits for Logic Simulation

#### 2.1.1 Modeling of Structure of Logic Circuits

In this thesis we mainly discuss gate-level logic circuits. Structure of a logic circuit is modeled by a directed graph. The nodes in the graph represent the primary inputs, the primary outputs and the gates of the circuit, and the edges represent connections among them. A primary input is represented by a nodes whose in-degree and out-degree is 0 and 1, respectively, while a primary output by a node whose in-degree and out-degree is 1 and 0, respectively. A node that represents a gate has nincoming edges and 1 outgoing edge. A function and delay are defined for a gate. We do not define them formally here, because it depends on the modeling of signal values, time and delay. We will refer to a circuit corresponding to an acyclic graph as a combinational circuit.

### 2.1.2 Modeling of Signal Values

In gate-level modeling of logic circuits, at least two signal values  $\theta$  and 1 are necessary so as to represent *logical zero* and *logical one*, respectively. The model of signal values which deals with the two values is called 2valued logic model and logic simulation based on the 2-valued logic model

|          |   |     |               |     |   | 0 | 1     | v    |     |    | 0 | 1 | Х | Ζ |

|----------|---|-----|---------------|-----|---|---|-------|------|-----|----|---|---|---|---|

|          |   | 0   | 1             |     | 0 |   | 1     |      | AND | 0  | 0 | 0 | 0 | 0 |

| AND      | 0 | 0   | 0             | AND | 0 | 0 | 0     | 0    |     | 1  | 0 | 1 | Х | 1 |

|          | 1 | 0   | 1             |     | 1 | 0 | 1     | X    |     | X  | 0 | х | Х | Х |

| NOT      |   | 1   | 0             |     | Х | 0 | X     | X    |     | Z  | 0 | 1 | Х | 1 |

| (a) 2-va |   | lue |               | NO  |   | 1 | 0     | Х    | NO  | Г  | 1 | 0 | X | 0 |

|          |   | (b  | (b) 3-valued. |     |   | L | (c) 4 | 1-va | lue | d. |   |   |   |   |

Fig. 2.1 Operation tables of AND and NOT operations.

is called 2-valued logic simulation. Fig. 2.1 (a) is the operation tables of AND and NOT operations in the 2-valued logic.

Although the 2-valued logic model may be sufficient for dealing with ideal logic circuits, we introduce in the practical logic simulation the following signal values for the purpose of modeling phenomena which are difficult to explain based on the 2-valued logic model or for the purpose of accelerating simulation execution. For the details, refer to [Bre76].

- Unknown value: It is introduced in order to represent signal values which are not definite and usually denoted as 'X' or 'U'. The unknown values are used in the following situations, for example.

- 1) Signal values on uninitialized signal lines (especially outputs of uninitialized flip-flops).

- 2) Output values of gates in response to illegal combinations of input values.

- 3) Output values of gates in response to don't care input values.

- 4) Signal values which are not logical 0 nor logical 1; in transition from one to the other, or in other states which can not be interpreted as logical 0 nor logical 1.

- 5) Signal values which can be 0 and 1 depending on delay values of gates.

- Signal values which can be indefinite because of the design errors.

The model which deals with 0, 1, and unknown value is referred to as a 3-valued logic model. Fig. 2.1 (b) is the operation tables for the 3-valued logic model. Although the unknown values provide many conveniences, they sometimes cause undesirable results. One of the problems is that the unknown values are used in so many contexts that they lead to unexpected simulation results. There should have been a clear distinction between the signal values which are not logical values and the ones which are indefinite but are logical values. It is pointed out that simulation results tend to be *pessimistic* in the current simulation techniques based on the 3-valued logic model, because it is based on the calculus in which  $X + \overline{X}$  comes to X instead of 1. We will discuss the modeling of indefinite signal values in detail in chapter 7.

- High-impedance value: It is introduced to express the output of tristate gates and usually denoted as 'Z'. The signal value system consisting of 0, 1, X(unknown) and Z is used in many logic simulators and is called a 4-valued logic model. The definition of the operation results associated with Z is dependent on the technologies that realize logic gates. Fig. 2.1 (c) is an example of the operation results.

- Transient values: They are introduced to distinguish rising and falling signals from erroneous states. They are denoted by 'R' and 'F', respectively, and often used in combination with the min/max delay model mentioned in the next subsection.

In addition, many kinds of signal values which indicate the possibilities

of undesirable signals which may caused by various design errors, such as hazards, signal conflict and so on.

On the other hand, as new attempts to extend logic simulation to formal verification, signal values represented by sets [Kim88, Ish90y] or Boolean functions [Car79, Cor81] have been proposed. Logic simulation based on the signal values represented by Boolean functions is called symbolic simulation.

#### 2.1.3 Modeling of Time

In gate-level logic simulation, we usually model time by a totally ordered set T. If  $T = \mathcal{Z}$  (the set of integers) the time model is called *discrete* time model and if  $T = \mathcal{R}$  (the set of real numbers) the model is called continuous time model. Most of the simulation algorithms and most of the existing logic simulators assume the discrete time model. A time period ticked by an integer is called a *unit time*.

On the other hand, there are approaches in which time is modeled by a *partially ordered set*[Sta85, Tes87]. This model is suitable for representing causality relationship or before-after relationship among events occurring in a circuit and suitable for modeling higher level design.

### 2.1.4 Modeling of Delay

Most of the existing delay models are based on the discrete time model. Followings are the classification of the delay models which are relevant to the discussions in this thesis.

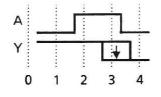

Zero delay model: It is a model in which all the delay values of the gates are zero. Here delay of zero means that the delay time is less than one if measured by the unit time but that there is causality relationship. This model is used when we are not interested in the timing issues on the circuit. It will cause difficulties in simulating logic circuits with feedback loops. Actually delay whose value is zero often causes undesirable situations. We will discuss the issue in chapter 7.

- Unit delay model: It is a model in which all the delay values of the gates are one.

- Assignable delay model: It is a model in which arbitrary delay values can be defined for each gate. it is further classified according to what type of delays are assigned.

Nominal delay model: A single delay value is assigned to a gate.

- *Rise/fall delay model:* Two delay values are defined to a gate, which represent delay values for  $0 \rightarrow 1$  transitions and for  $1 \rightarrow 0$  transitions.

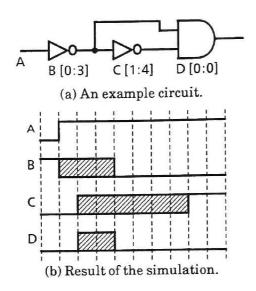

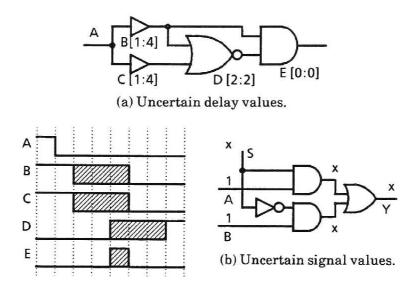

- $Min/max \ delay \ model:$  In actual logic circuits, delay values of gates vary depending on the difference of process conditions or usage conditions. In order to express this uncertainty the delay value is specified by its minimum and maximum values  $d^{min}$  and  $d^{max}$ , respectively. When a signal change occurs at time t, the output signal value at time between  $t + d^{min}$  and  $t + d^{max}$  becomes X (unknown) or transient signal values, as shown in Fig. 2.2. Although this model is based on the very realistic assumption, it has been pointed out that this model has serious shortcomings such that simulation results are often too pessimistic due to reconvergent fanouts [Bre76]. For example, in Fig. 2.2, the unknown states on the output of D indicate the possibility of a static hazard, which never occurs in an actual circuit. We will discuss this issue in detail in chapter 5 and chapter 6.

In actual circuits realized as integrated circuits, delay values of connections among gates are much large than those of gates. In this thesis,

Fig. 2.2 Min/max delay simulation.

however, we assume delay only on gates because the delay of a connection can be expressed by inserting a buffer gate with the delay.

#### 2.1.5 Logic Simulation

Logic simulation is to compute the signal value sequences on the primary outputs for given descriptions of a logic circuit and signal value sequences on the primary inputs. Formal definition of logic simulation depends on models of signal value, time and delay. We show a definition of the case of the 2-valued logic, discrete time and assignable nominal delay model, as an example.

A sequence of signal values on node  $n_i$ , which represents a primary input, a primary output or a gate, is modeled as mapping  $v_i : \mathcal{P} \to \mathcal{B}$ , where  $\mathcal{P}$  is the set of the non-negative integers and  $\mathcal{B} = \{0, 1\}$ . Let  $n_i^1$ ,  $n_i^2, \dots, n_i^{m_i}$  be nodes which are the direct predecessor of node  $n_i$  and  $v_i^1$ ,  $v_i^2, \dots, v_i^{m_i}$  be the signal value sequences on  $n_i^1, n_i^2, \dots, n_i^{m_i}$ , respectively. Function  $f_i$  and delay value  $d_i$  are defined for node  $n_i$ , where  $f_i : \mathcal{B}_i^m \to \mathcal{B}$ and  $d_i \in \mathcal{P}$ . As for nodes representing primary outputs, assume the identity function as  $f_i$ . Then the following relation holds for each node  $n_i$ .

$$v_i(t - d_i) = f_i(v_i^1(t), v_i^2(t), \cdots, v_i^{m_i}(t)).$$

(2.1)

Logic simulation is to compute  $v_i$  for each of the primary output  $n_i$  for given sequences of signal values on the primary outputs.

## 2.2 Basic Algorithms for Logic Simulation

# 2.2.1 Compiler-Driven Simulation and Event-Driven Simulation

We can classify the algorithms of logic simulation into *compiler-driven* methods and *event-driven methods*. The compiler-driven method is a simple algorithm in which logic simulation is executed by computing at each time the formula (2.1) for each node. We refer to the computation of the Boolean function of a gate to an *evaluation* of the gate. We have to pay attention to the order of gate evaluation. In the case of combinational circuits, the order of gate evaluation is usually determined before simulation execution (the details are described in subsection 2.2.4). If a given circuit has feedback loops, it happens that the correct signal value of a node at a certain time is not properly computed by simply evaluate each gate once. In such cases, we usually continue computation until the signal values are stable. If the computation does not stop because of oscillations, simulator detects this and outputs error messages.

Although the compiler-driven simulation algorithm is simple and easy to implement, we are forced to evaluate gates whose input values are the same as the previous values. Signal values do not change so often; the ratio of the signal change is  $1\sim10\%$  or less than that. The eventdriven simulation algorithm attempts to reduce the computation cost by evaluating only the gates whose input values are different from those at the previous time period. A change of a signal value is called an *event*. Although extra cost is required to manage events, event-driven simulation is more efficient than compiler-driven simulation especially in handling assignable delay models.

Simulation speed is measured in terms of gate evaluations per second in compiler-driven simulation and events per second in event-driven simulation.

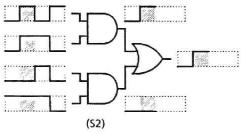

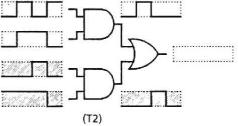

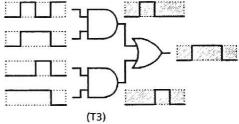

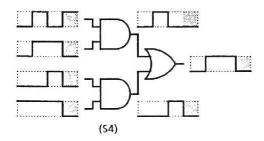

#### 2.2.2 S-Algorithm and T-Algorithm

We can classify algorithms of logic simulation also from the standpoint if they are based on space first evaluation or time first evaluation [Ish84, Ish85yy]. The space first evaluation is a strategy in which time is advanced after finishing all the necessary evaluation of gates at a time frame, while time first evaluation is a strategy in which all the possible computation on a gate is performed in time direction for each gate (see Fig. 2.3). We abbreviate an algorithm based on the space first evaluation to *S*-algorithm and on time first evaluation to *T*-algorithm. We can consider four types of algorithms for the combinations of the two strategies in the previous subsection (compiler-driven and event-driven) and the two strategies in this section (S-algorithms and T-algorithms).

## (1) Compiler-driven simulation based on the S-algorithm

We assume that the order of gate evaluation is determined before simulation by a method described in 2.2.4. We also assume that time begins with 0 and the final time at which we stop simulation is given.

- 1) Repeat 2) for each time from 0 to the final time.

- 2) Repeat 3) until signal values of all nodes become stable.

- 3) Evaluate gates in the predetermined order.

### S-Algorithm

T-Algorithm

(S3)

Fig. 2.3 S-algorithm and T-algorithm.

Note that in the case of combinational circuit, the signal values become stable by the first execution of 3) if gates are evaluated in the order described in 2.2.4.

#### (2) Event-driven simulation based on the S-algorithm

Events whose occurrences are known are maintained in set S.

- 1) Repeat 2) for each time t from 0 to the final time.

- 2) Take out events whose occurrence time is t and perform 3) for each event.

- Evaluate the gates which are affected by the event. If there are signal changes, generate new events and include them in S.

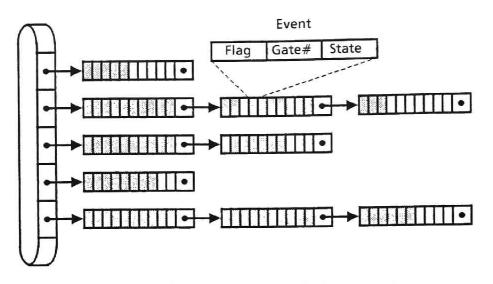

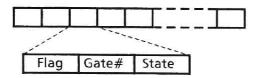

In order to maintain events, we use a data structure called *time wheel*, which consists of linear lists of events and an array of headers to the linear lists. Each list consists of the events which are know to occur at the same time frame. This data structure is suitable for efficient extraction of events in 2) and registration of events in 3).

## (3) Compiler-driven simulation based on the T-algorithm

We assume that the order of gate evaluation is predetermined.

- 1) Repeat 2) until all the signal values become stable.

- 2) Repeat 3) for each gate in the predetermined order.

- 3) Perform gate evaluation for all the possible time frames.

Note that in the case of combinational circuit, the signal values become stable by the first execution of 2).

# (4) Event-driven simulation based on the T-algorithm

In this algorithm [Ish84, Ish85yy], a sequence of signal values are represented by a linear list of events, where an event is a tuple of time and a signal value.

- 1) Execute 2) for each gate in the predetermined order.

- 2) Repeat 3)  $\sim$  4) until there is no processed event at input lines.

- 3) Among the events which may occur next at input lines, select an event whose occurrence time is the smallest, and compute the effect of the event.

- 4) If the output value of the gate changes as a result of 4), add an event to the output line whose occurrence time is a sum of occurrence time of the input event and the delay of the gate.

Most of the existing simulators are based on S-algorithms because it is difficult to deal with circuits with feedback loops in T-algorithms. However, T-algorithms are attractive in dealing with combinational circuits because they are simple and much more efficient than S-algorithms in simulating combinational circuits. Espacially, it was discovered independently by [Bar87, Koe86, Ish87] that combination of T-algorithm based compiler-driven simulation and *bit-parallel* gate evaluation technique [Bre76] is a very efficient simulation technique for combinational circuit. It is also shown that event-driven simulator based on the Talgorithm is 7 ~ 8 times faster than that on the S-algorithm [Ish84, Ish85yy].

# 2.2.3 Code Generation Method and Table-Driven Method

The following two methods are know as ones for implementing logic simulators.

- **Code-generation method:** Generate a code (for computers) to realize gate evaluation and perform simulation by executing the code.

- Table-driven method: Generate tables containing information necessary for simulation such as an order of gate evaluation, the kind of each gate and connections among the gates. Perform simulation by referring the table. In the compiler-driven simulation, this method can be regarded as an *interpreter*-driven method.

Generally the code-generation method enables faster simulation execution than table-driven method. The compiler-driven method has good affinity for code generation method. Actually, the compiler-driven simulators in the early times were implemented by this method which is the origin of the name *compiler-driven* method. On the other hand, it is considered to be difficult to implement event-driven simulators based on the code-generation method.

#### 2.2.4 Ordering of Gate Evaluations

In compiler-driven simulation and T-algorithms, an order of gate evaluation is important because we can dispense with futile gate evaluation if we choose a good order. Furthermore it causes a big difference in the storage requirement for simulation as is discussed in chapter 3.

The most popular method of ordering is the one called *level sorting* [Bre76]. In this method gates are ordered according to *level numbers* of gates. The level number  $l(n_i)$  of gate  $n_i$  is defined as follows based on the notation in the previous section.

$$l(n_i) = \begin{cases} 0 & \text{if } n_i \text{ is a primary input} \\ 1 + \max\{l(n_i^1), l(n_i^2), \cdots, l(n_i^{m_i})\} & \text{otherwise.} \end{cases}$$

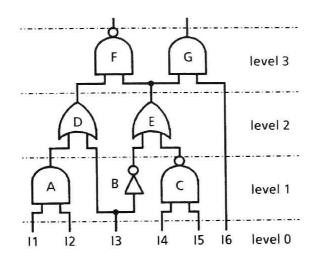

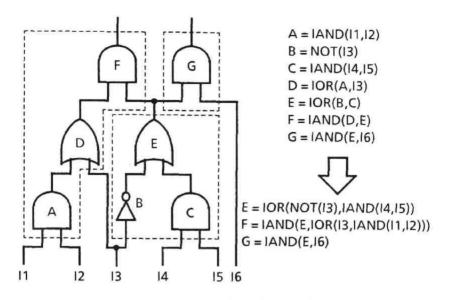

For example, in Fig. 2.4, A - B - C - D - E - F - G and B - C - A - E - D - F - G are obtained in this ordering.

Fig. 2.4 Ordering of gate evaluation.

As a generalization of level sorting, we consider data flow sorting (DF-sorting) [Ish87, Ish86]. An available gate is a gate whose all input values have already been computed. Let S be the set of available gates. Then the order of gate evaluation is determined by the following procedure.

- At the beginning, include the gates with its all inputs connected to the primary inputs in S.

- 2) Repeat 3) and 4) until S becomes empty.

- 3) Get gate g out of S and evaluate g.

- 4) After the evaluation of g, if any gates become newly available, add them to S.

By DF-sorting we can get any of the all orders that yield correct simulation result. In Fig. 2.4, A - D - B - C - E - F - G and B - C - E - G - A - D - F are the examples of order obtained by DF-sorting but not by level sorting. The DF-sorting provides us a higher degree of freedom to allow wide choice in determining the gate evaluation order than level sorting. We will use this freedom for reducing the storage requirement for simulation in chapter 3 and chapter 4.

# Chapter 3

# Fast Logic Simulation Using Vector Super Computers

# 3.1 Introduction

Computation time required for logic simulation is roughly proportional to the size of a circuit under test and to the length of test patterns. The increase in the circuit size, together with the incidental increase in the test pattern size, has resulted in the rapid growth of the computation time for the simulation. It is one of the most important subjects in the area of Computer-Aided Design (CAD) for Very Large Scale Integration (VLSI) to develop high-speed logic simulation techniques. In this chapter, we propose logic simulation techniques using vector processors, as a new approach to accelerating simulation speed.

In order to reduce simulation time, a number of research efforts have been carried out in recent years. These approaches can be roughly classified into the following kinds.

Contrivance on the circuit modeling: The function level modeling and the function level simulation, for example, bring forth the drastic reduction in computation time and in storage requirements (in exchange for a precision, however).

- Improvements in simulation algorithms: The concurrent simulation technique [Ulr83], clock suppression [Ulr83] and time first evaluation algorithm (T-algorithm) [Ish84, Ish85yy] are such examples.

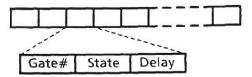

- 3) Techniques in coding: Zoom table look-up [Ulr80b] is one of the most popular coding techniques. The vector coding technique for a scalar processor by Krohn [Kro81], though it is in some way analogous to our approach, also falls under this category.

- 4) Development of special purpose hardware (hardware simulation engines): Several types of hardware simulation engines have been designed and some of them (YSE by IBM [Den83], HAL by NEC [Sas83], and Logic Evaluator by ZYCAD [Bla84], VELVET by Hitachi [Nag86], SP by Fujitsu [Hir87], for example) have actually been implemented and are in practical use.

Using parallel computation schemes, the hardware approach has demonstrated the potential to improve performance by a factor of 1000 over current software solutions. However, software simulators may be as fast as hardware simulators, if the power of the fastest computers, or super computers, can be efficiently harnessed. Furthermore, software is generally more flexible and portable than hardware. From an engineering standpoint, there are many benefits to developing a software simulation method with performance comparable to that of current hardware solutions.

A vector processor is a supercomputer which has the facility to execute operations on vectors extremely fast. Several vector processors have been developed in recent years [Lub85], which are capable of executing several hundred MFLOPS (Million FLoating-point Operations Per Second). Vector processors are developed with a view to accelerating the numerical computation for problems that require enormous computation power. In addition to the powerful facilities for floating-point operations, they have vector operations so versatile that we can use their computation power in many applications.

We must note that all programs cannot enjoy the benefit of vector processors. High vectorization ratio, and yet long vector length are essential for efficient computation. We must tune up our coding schemes or basic algorithms to be suitable for vector processing.

In this chapter, we propose new high-speed logic simulation techniques which efficiently utilize the computation power of vector processors [Ish85ykv, Ish85yki, Ish86, Ish87]. We have developed 3 types of simulation techniques which are dedicated for:

- 1) zero-delay simulation of combinational circuits,

- 2) zero-delay simulation of synchronous sequential circuits, and

- 3) simulation with delay consideration.

The first two are based on the compiler-driven method and the last on the event-driven method.

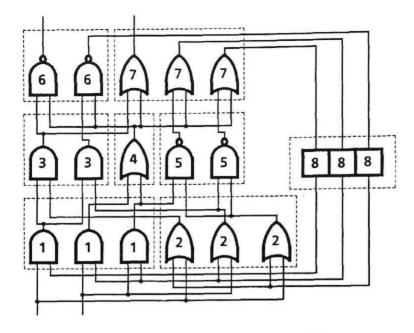

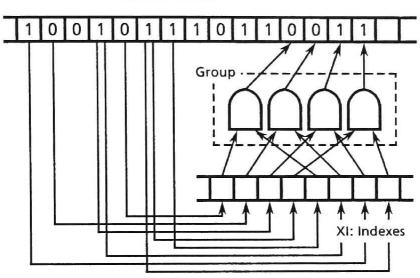

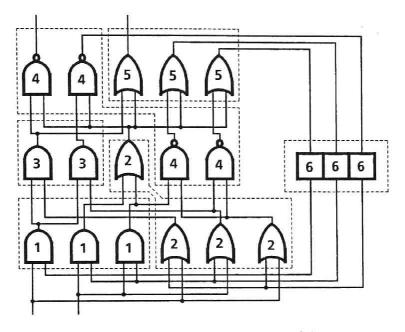

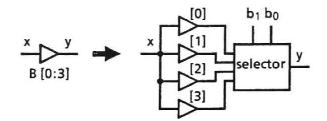

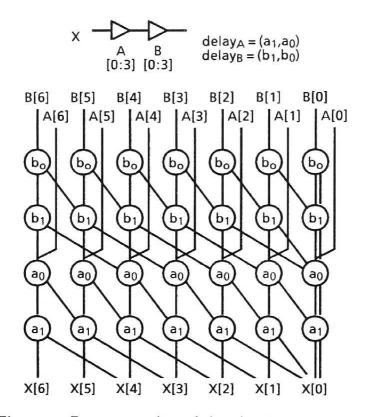

For the simulation of combinational circuits, we propose vector-parallel simulation technique (VP-technique), which is based on the time first evaluation algorithm (T-algorithm) [Ish84, Ish85yy]. A sequence of states on a signal line is treated as a vector (a pattern vector) and the gate evaluation is performed by vector logical operations on pattern vectors. For the simulation of synchronous sequential circuits, the simulation procedure is vectorized by a gate grouping technique (GG-technique), which is based on the space first evaluation algorithm (S-algorithm). In this case, we increase the vectorization ratio by grouping gates of the same kind and evaluating them together in a vectorized manner.

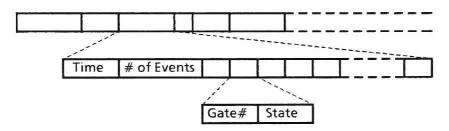

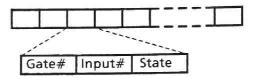

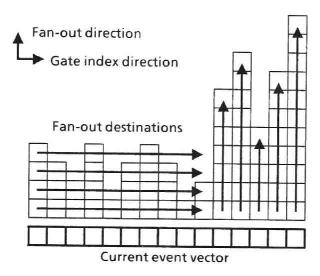

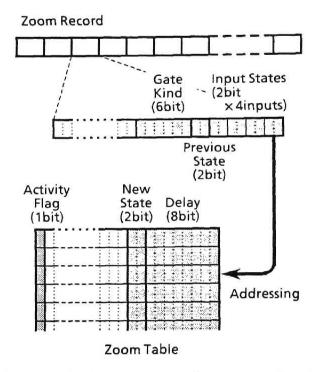

In order to carry out the timing simulation with sophisticated delay models, we have also developed a vectorization technique for event-driven simulation. The algorithm we adopted is basically the conventional eventdriven method with a time mapping technique. The procedures for event fetch, event propagation, gate evaluation and event registration are vectorized by processing all the events together which are scheduled to occur at the same period. Data structures and the operations on events are modified to be suitable for vector processing.

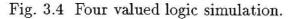

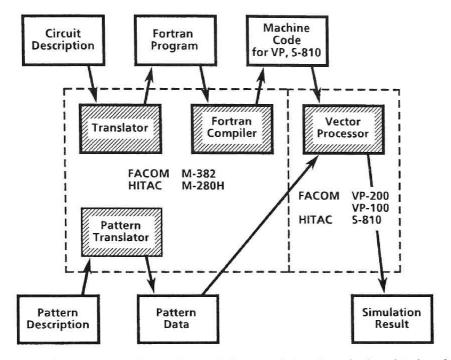

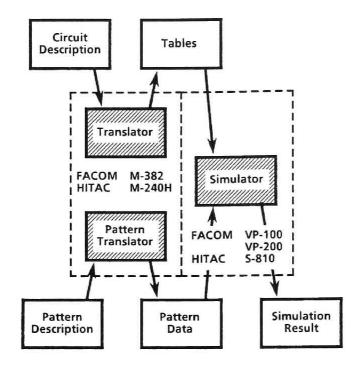

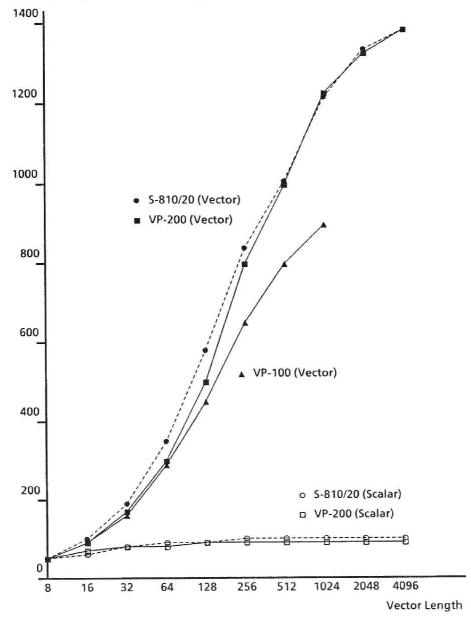

We have implemented logic simulators based on the above simulation techniques on the FACOM VP-100 and VP-200 (266 MFLOPS and 533 MFLOPS, respectively) at Kyoto University and the HITAC S-810/20 (630 MFLOPS) at the University of Tokyo. The maximum performance is about  $7.7 \times 10^9$  gate-evaluations per second for combinational circuit simulation,  $1.4 \times 10^9$  gate-evaluations per second for sequential circuit simulation (by the VP-200) and  $230 \times 10^3$  events per second for eventdriven simulation (by the S-810/20). This performance is comparable to that of hardware simulation engines. Moreover, our techniques are so straightforward that we can implement them on most of the recent vector processors without serious modifications.

In the next section, we provide an overview of some important features of vector processors The two sections that follow are devoted to an explanation and consideration of the simulation techniques based on the compiler- driven method. Section 3.3 deals with the simulation of combinational circuits and Section 3.4 with the simulation of synchronous sequential circuits. A vector processor oriented technique for event-driven simulation is stated in Section 3.5. The last section concludes this chapter with some comments.

# 3.2 Vector Supercomputers

Vector processors are supercomputers which have been developed to meet the requirements for large scale computation in such area as hydrodynamics, numerical weather prediction, and nuclear energy research. Computation speed is increased by executing the uniform operations on array structured data using functional pipeline units. Main storage has a large capacity of several hundred mega bytes and is designed to afford enough access speed to balance the high throughput of the functional pipeline units. The maximum performance of recent vector processors reaches several MFLOPS (Million FLoating-point Operations Per Second) [Lub85], ten to hundred times faster than the largest general purpose computers.

Although the maximum performance of vector processors is very high, this performance is available only when almost all the operations in a program are executed by vector instructions. The execution speed will degenerate in accordance with the decrease of vectorization ratio, which is defined as the rate of the operations executed by vector instructions to all the operations. Let us define vector execution of a program as executing possible operations by vector instructions, scalar execution of a program as executing all the operations by scalar instructions and acceleration ratio of a program as the ratio of the execution speed by vector execution to that by scalar execution. When the vectorization ratio is 50 percent, acceleration ratio can not exceed 2.0 no matter how efficient the vector instructions are. Acceleration ratio increases markedly when vectorization ratio goes by 90 percent.

Another important factor to be considered is *vectorlength*. Since the overhead for setting up a vector instruction is considerably large, enough efficiency is not available if the operand vectors are short. (Sometimes vector instruction becomes less efficient than scalar instruction). Moreover, the execution speed is also swayed by such factors as the type of memory accesses, the type of instructions and the number of pipelines which can operate in parallel. With due regard to the above factors, we have not only to tune up the coding schemes but also to choose, modify or newly design basic algorithms so that the programs will be suitable for vector processing.

Table 3.1 summarizes the specification of the FACOM VP-100, VP-

Table 3.1 Specification of vector supercomputers.

|                                       | FACOM VP-100                                                | FACOM VP-200                                                | HITAC S-810/20                                                                |

|---------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|

| Instruction                           | 82-vector<br>195 scalar                                     | 82 vector<br>195 scalar                                     | 83 vector<br>195 scalar                                                       |

| Functional<br>Pipelines               | add/logical<br>multiply<br>divide<br>mask<br>load/store×2   | add/logical<br>multiply<br>divide<br>mask<br>load/store×2   | add/logical<br>multiply+add<br>multiply/divide+add<br>mask<br>load×2<br>store |

| Pipeline cycle                        | 7.5ns                                                       | 7.5ns                                                       | 15ns                                                                          |

| Vector Register                       | 32KB                                                        | 64KB                                                        | 64KB                                                                          |

| Maximum<br>Capacity of<br>Main Memory | 128MB                                                       | 256MB                                                       | 256MB                                                                         |

| Peak CPU<br>Speed                     | 266MFLOPS                                                   | 533MFLOPS                                                   | 630MFLOPS                                                                     |

| Vectorizing<br>Facilities             | Fortran77/VP<br>Compilers<br>with Interactive<br>Vectorizer | Fortran77/VP<br>Compilers<br>with Interactive<br>Vectorizer | Fortran77 HAP<br>Compilers                                                    |

200 and the HITAC S-810/20, new vector processors on which we have developed our logic simulators. They have many advanced features making it versatile for a wide range of applications. The functional pipeline units can afford not only floating point operations but also fixed-point operations and bit-wise logical operations. The load/store pipeline, which transfers data between the main storage unit and vector registers, can afford three types of vector accesses:

- a) contiguous vector access,

- b) constant stridden vector access, and

- c) indirectly addressed vector access.

As for the access speed, (a) is the fastest and (c) is the slowest. The indirectly addressed vector access allows an operation coded in the following FORTRAN statements to be vectorized and executed efficiently.

DO 10 I=1,N 10 A(I)=B(L(I))

Where the array L is an array of integers. This facility is particularly appropriate to the vectorization of table look-ups in the logic simulation.

In addition, these vector processors are capable of handling DO loops containing the conditional statements.

DO 20 I=1,N 20 IF (A(I).GT.O.O) B(I)=B(I)+C(I)

Another powerful vector function is a *vector compress function*, which gathers the elements of a vector whose corresponding subscripts satisfy certain conditions. We can use this function by the following coding.

```

K=0

D0 30 I=1,N

IF (A(I).GT.0.0) THEN

K=K+1

C(K)=B(I)

ENDIF

30 CONTINUE

```

This function plays a very important part in the event-driven simulation to be discussed in Section 5.

As well as the above powerful vector processing facilities, these vector processor have very large main storage. The maximum capacity of the main storage is 256M bytes (VP-200 and S-810/20) and 128M bytes (VP-100).

# 3.3 Vectorization of Combinational Circuit Simulation

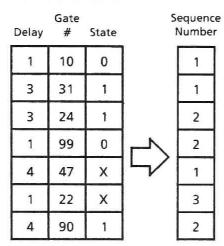

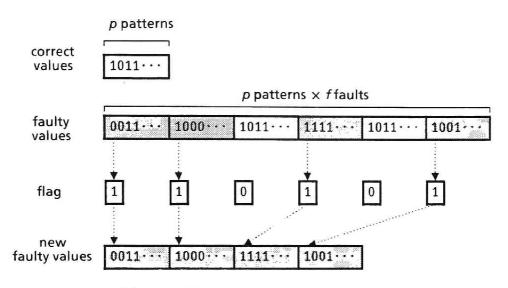

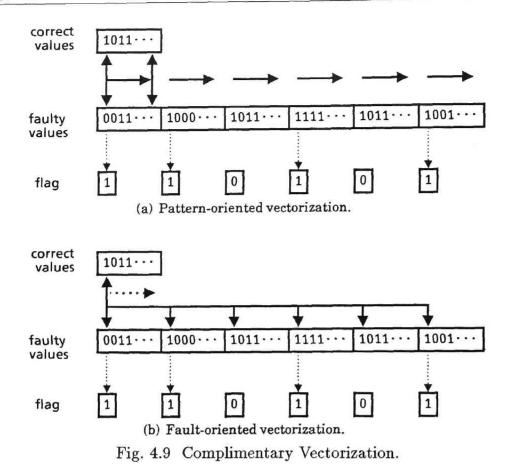

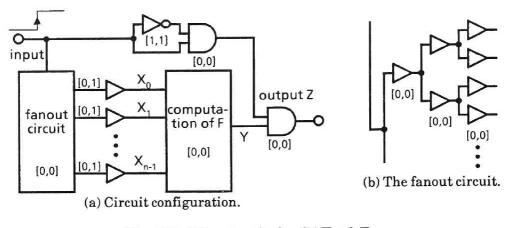

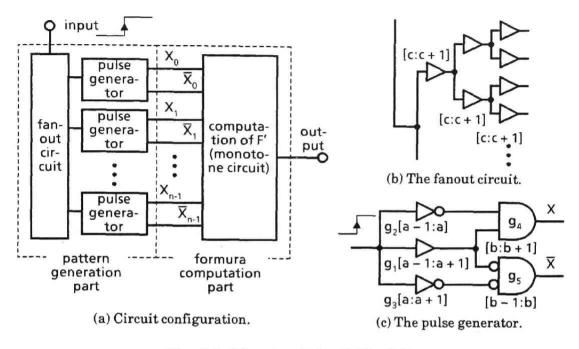

## 3.3.1 Vector-Parallel Simulation Technique