INCH - POUND

MIL-STD-750D 28 FEBRUARY 1995 SUPERSEDING MIL-STD-750C 23 FEBRUARY 1983

# MILITARY STANDARD TEST METHODS FOR SEMICONDUCTOR DEVICES

Test Methods for Semiconductor Devices.

# MIL-STD-750D

- 1. This Military Standard is approved for use by all Departments and Agencies of the Department of Defense.

- 2. Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to: Commander, Defense Supply Center Columbus, ATTN: DSCC-VAT, 3990 E. Broad Street, Columbus, OH 45316 by using the Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter.

- 3. Entire standard revised.

# CONTENTS

|           |                                                                                                                                                                                                  | CONTENTO                                                                                                                                                              | <u>Page</u>                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Paragraph | 1.                                                                                                                                                                                               | SCOPE                                                                                                                                                                 | 1                                                                                                                              |

|           | 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.3                                                                                                                                                              | Purpose Numbering system Classification of tests Revisions Method of reference.                                                                                       | 1<br>1<br>1<br>1                                                                                                               |

|           | 2.                                                                                                                                                                                               | APPLICABLE DOCUMENTS                                                                                                                                                  | 2                                                                                                                              |

|           | 2.1<br>2.1.1<br>2.1.2<br>2.2<br>2.3                                                                                                                                                              | Government documents Specifications, standards, and handbooks Other Government documents, drawings, and publications Non-Government publications Order of precedence. | 2<br>2<br>2<br>3<br>3                                                                                                          |

|           | 3.                                                                                                                                                                                               | DEFINITIONS                                                                                                                                                           | 4                                                                                                                              |

|           | 3.1<br>3.1.1                                                                                                                                                                                     | Abbreviations, symbols, and definitions                                                                                                                               | 4<br>4                                                                                                                         |

|           | 4.                                                                                                                                                                                               | GENERAL REQUIREMENTS                                                                                                                                                  | 5                                                                                                                              |

|           | 4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.3.1<br>4.1.4<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.4.1<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>4.3.8.1<br>4.3.8.2<br>4.4.1<br>4.5<br>4.6 | Test conditions Permissible temperature variation in environmental chambers Electrical test frequency                                                                 | 5<br>5<br>5<br>5<br>5<br>5<br>6<br>6<br>6<br>7<br>7<br>7<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>9<br>9<br>9<br>9<br>9<br>9 |

|           | 5.                                                                                                                                                                                               | DETAILED REQUIREMENTS                                                                                                                                                 | 11                                                                                                                             |

|           | 6.                                                                                                                                                                                               | NOTES                                                                                                                                                                 | 12                                                                                                                             |

|           | 6.1                                                                                                                                                                                              | International standardization agreement                                                                                                                               | 12                                                                                                                             |

|           |                                                                                                                                                                                                  | FIGURES                                                                                                                                                               |                                                                                                                                |

| Figure    | 1.<br>2.                                                                                                                                                                                         | Orientation of noncylindrical semiconductor device to direction of accelerating force                                                                                 | 7<br>7                                                                                                                         |

| Index     |                                                                                                                                                                                                  | Numerical index of test methods                                                                                                                                       | 15                                                                                                                             |

### 1. SCOPE

- 1.1 <u>Purpose</u>. This standard establishes uniform methods for testing semiconductor devices, including basic environmental tests to determine resistance to deleterious effects of natural elements and conditions surrounding military operations, and physical and electrical tests. For the purpose of this standard, the term "devices" includes such items as transistors, diodes, voltage regulators, rectifiers, tunnel diodes, and other related parts. This standard is intended to apply only to semiconductor devices. The test methods described herein have been prepared to serve several purposes:

- a. To specify suitable conditions obtainable in the laboratory that give test results equivalent to the actual service conditions existing in the field, and to obtain reproducibility of the results of tests. The tests described herein are not to be interpreted as an exact and conclusive representation of actual service operation in any one geographic location, since it is known that the only true test for operation in a specific location is an actual service test at that point.

- b. To describe in one standard all of the test methods of a similar character which now appear in the various joint-services semiconductor device specifications, so that these methods may be kept uniform and thus result in conservation of equipment, manhours, and testing facilities. In achieving this objective, it is necessary to make each of the general tests adaptable to a broad range of devices.

- c. The test methods described herein for environmental, physical, and electrical testing of devices shall also apply, when applicable, to parts not covered by an approved military sheet-form standard, specification sheet, or drawing.

- 1.2 <u>Numbering system</u>. The test methods are designated by numbers assigned in accordance with the following system:

- 1.2.1 <u>Classification of tests</u>. The tests are divided into five areas. Test methods numbered 1001 to 1999 inclusive, cover environmental tests; those numbered 2001 to 2999 inclusive cover mechanical- characteristics tests. Electrical- characteristics tests are covered in two groups; 3001 to 3999 inclusive covers tests for transistors and 4001 to 4999 covers tests for diodes. Test methods numbered 5000 to 5999 inclusive are for high reliability space applications.

- 1.2.2 <u>Revisions</u>. Revisions are numbered consecutively using a period to separate the test method number and the revision number. For example, 4001.1 is the first revision of test method 4001.

- 1.3 <u>Method of reference</u>. When applicable, test methods contained herein shall be referenced in the individual specification by specifying this standard, the method number, and the details required in the summary of the applicable method. To avoid the necessity for changing specifications that refer to this standard, the revision number should not be used when referencing test methods. For example, use 4001, not 4001.1.

### 2. APPLICABLE DOCUMENTS

2.1 General. The documents listed in this section are specified in sections 3 and 4 of this standard. This section does not include documents cited in other sections of this standard or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements documents cited in sections 3 and 4 of this specification, whether or not they are listed.

## 2.2 Government documents.

2.2.1 <u>Specifications, standards, and handbooks</u>. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DODISS) and supplement thereto, cited in the solicitation (see 6.2)

### **SPECIFICATIONS**

**MILITARY**

MIL-S-19500 - Semiconductor Devices, General Specification for.

## **STANDARDS**

## **MILITARY**

MIL-STD-12 Abbreviations for used on Drawings, Specification Standards & in Technical

MIL-STD-202 MIL-STD-45662 MIL-STD-1686 Test Methods for Electronic and Electrical Component Parts.

Calibration Systems Requirements.

Electrostatic Discharge Control Program for Protection of Electrical and Electronic Parts, Assemblies and Equipment (Excluding Electrically Initiated

Explosive Devices) (Metric).

# **HANDBOOKS**

**MILITARY**

Electrostatic Discharge Control Handbook for Protection of Electrical and MIL-HDBK-263

Electronic Parts, Assemblies and Equipment (Excluding Electrically Initiated

Explosive Devices) (Metric).

(Unless otherwise indicated, copies of federal and military specifications, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Bldg. 4D, Philadelphia, PA 19111-5094.)

2.1.2 Other Government documents, drawings, and publications. The following other Government documents, drawings, and publications form a part of this document to the extent specified herein. Unless otherwise specified, the issues are those cited in the solicitation.

## **DRAWINGS - JAN**

103-JAN

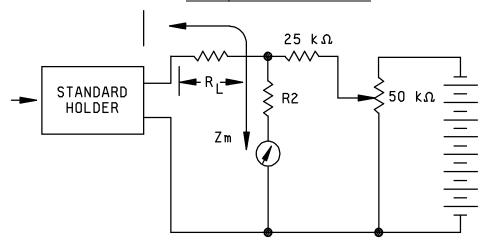

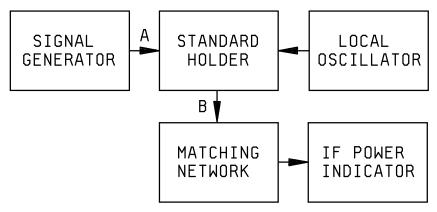

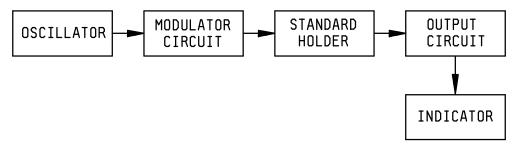

Filter for Testing Crystal Rectifier 1N23, 1N23A and 1N23B. Mixer for Testing Crystal Rectifier Type 1N26. Figure of Merit Holder for Crystal Rectifier 1N31. Mixer and Coupling Circuit for Crystal Rectifiers 1N21B. SA Band Crystal Detector Test Holder. 107-JAN 118-JAN

124-JAN

152-JAN

174-JAN

231-JAN

Mixer for Electron Tube Type 1N53.

Burn Out Testing Equipment for 1N25 Crystals Schematic Diagram.

Loss Measuring Equipment for 1N25 Crystals Schematic Diagram.

Loss Measuring Equipment for 1N25 Crystals Bill of Material. 233-JAN 234-JAN

Burn Out Testing Equipment for 1N25 Crystals Bill of Materials. Reverse Pulse Recovery Time Test and Calibration Procedure. Mixer Holder, Narrow, Band, for 1N263. 236-JAN

256-JAN 266-JAN

# **DRAWINGS - DESC ASSEMBLY**

D64100

Diode Test Holder, 3,060 MHz (S-Band). Sliding Load (S-Band) Used with D64100. Assembly, Tri-polar Diode Holder. C64169 C65017

Diode Test Holder, 9,375 GHz (X-Band). Sliding Load (X-Band) Used with D65019. Diode Test Holder, 16 GHz (Ku-Band). Sliding Load (Ku-Band) Used with D65064. D65019 C65042 D65064

C65101 Mixer Holder, Narrow Band, for 1N1838. Adaptor For Burn-Out Test. Burn-Out Tester For Microwave Diodes. C66053

B66054

C66058

(Copies of drawings may be obtained from the Defense Supply Center Columbus, (DSCC-VAT), 3990 E. Broad Street, Columbus, Ohio 45316. When requesting copies of these drawings, both the identifying symbol number and title should be stipulated.)

2.2 Non-Government publications. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DoD adopted are those listed in the DODISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation (see 6.2).

Standard Handbook for Electrical Engineers.

(Application for copies should be addressed to the McGraw-Hill Book Company, Inc., New York, N.Y. 42840.)

NBS Handbook 59 - Permissible Dose From External Sources of Ionizing Radiation, Recommendations of National Committee on Radiation Protection.

NBS Handbook 73 - Protection Against Radiations from Sealed Gamma Sources. NBS Handbook 76 - Medical X-Ray Protection Up to 3 Million Volts.

(Application for copies should be addressed to the Superintendent of Documents, Washington, DC 20402.)

2.3 Order of precedence. In the event of a conflict between the text of this document and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

# 3. DEFINITIONS

- 3.1 <u>Abbreviations, symbols, and definitions</u>. For the purposes of this standard, the abbreviations, symbols, and definitions specified in MIL-S-19500, MIL-STD-12, and herein shall apply.

- 3.1.1 Abbreviations used in this standard. Abbreviations used in this standard are defined as follows:

- a. ATE Automatic test equipment.

- b. BIST Backward instability shock test.

- c. DPA Destructive physical analysis.

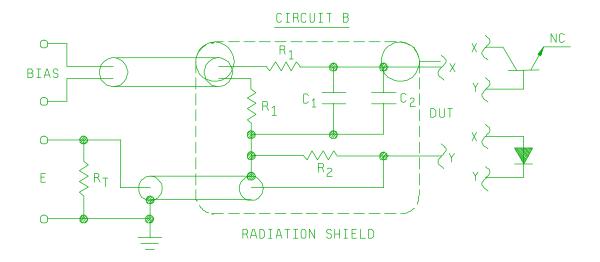

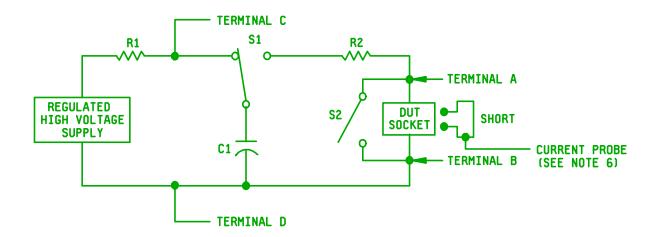

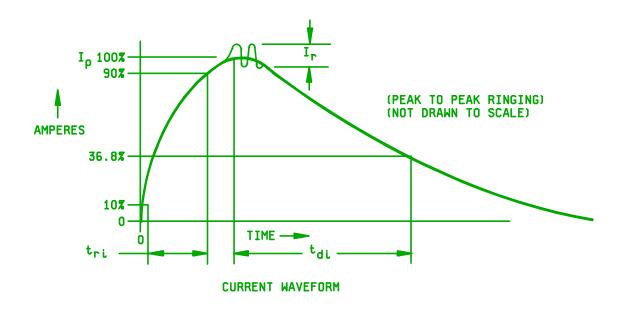

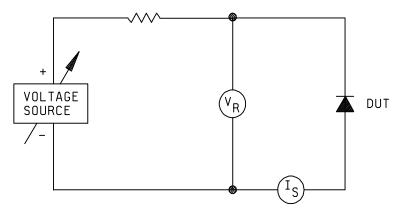

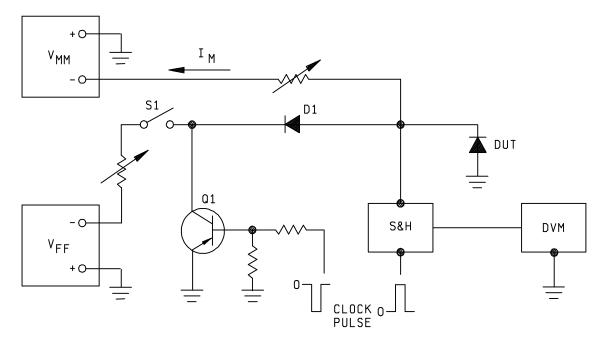

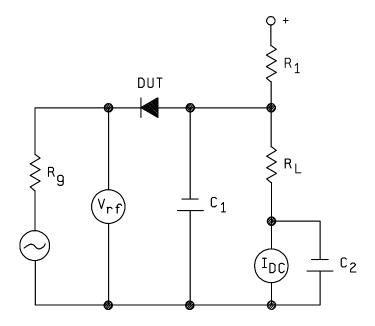

- d. DUT Device under test.

- e. ESD Electrostatic discharge.

- f. ESDS Electrostatic discharge sensitivity.

- g. FET Field-effect transistor.

- h. FIST Forward instability shock test.

- i. FWHM Full-width half-max.

- j. HTRB High temperature reverse bias.

- k. IF Intermediate frequency.

- I. IGBT Insulated gate bipolar transistor.

- m. LCC Leadless chip carrier.

- n. LINAC Linear accelerator.

- o. MOSFET Metal oxide semiconductor field-effect transistor.

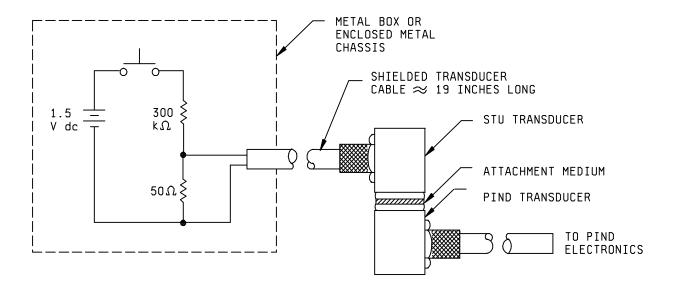

- p. PIND Particle impact noise detection.

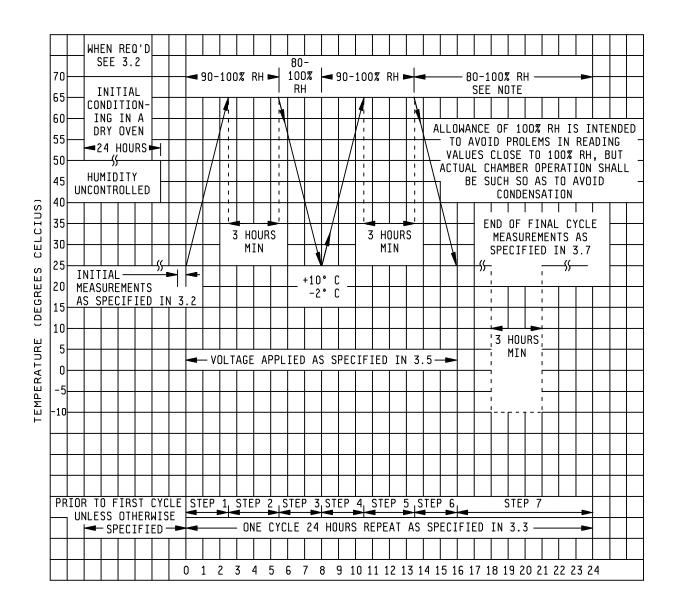

- q. RH Relative humidity.

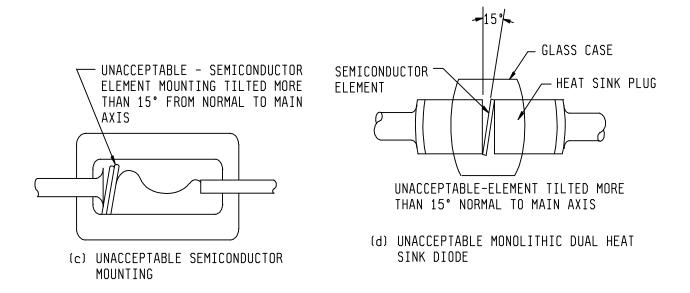

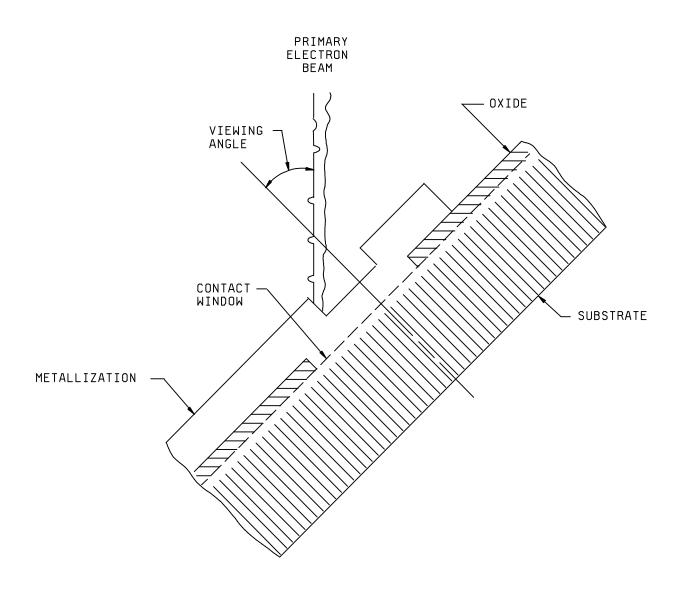

- r. SEM Scanning electron microscope.

- s. SOA Safe operating area.

- t. SSOP Steady-state operating power.

- u. STU Sensitivity test unit.

- v. SWR Standing wave ratio.

- w. TLD Thermoluminescence dosimetry.

- x. TSP Temperature sensitive parameter.

# 4. GENERAL REQUIREMENTS

- 4.1 <u>Test conditions</u>. Unless otherwise specified herein or in the individual specification, all measurements and tests shall be made at thermal equilibrium at an ambient temperature of  $25^{\circ}$ C  $\pm 3^{\circ}$ C and at ambient atmospheric pressure and relative humidity and the specified test condition C (at environmentally elevated and reduced temperatures) shall have a tolerance of  $\pm 3$  percent or  $\pm 3^{\circ}$ C, whichever is greater. Whenever these conditions must be closely controlled in order to obtain reproducible results, the referee conditions shall be as follows: temperature  $25^{\circ}$ C  $\pm 10^{\circ}$ C, relative humidity  $50^{\circ}$   $\pm 5^{\circ}$  percent, and atmospheric pressure from 650 to 800 millimeters of mercury. Unless otherwise specified in the detail test method, for mechanical test methods, 2000 series, the ambient temperature may be  $25^{\circ}$ C  $\pm 10^{\circ}$ C.

- 4.1.1 <u>Permissible temperature variation in environmental chambers</u>. When chambers are used, specimens under test shall be located only within the working area defined as follows:

- a. Temperature variation within working area: The controls for the chamber shall be capable of maintaining the temperature of any single reference point within the working area within ±2°C or ±4 percent, whichever is greater.

- b. Space variation within working area: Chambers shall be so constructed that, at any given time, the temperature of any point within the working area shall not deviate more than ±3°C or ±3 percent, whichever is greater, from the reference point, except for the immediate vicinity of specimens generating heat.

- c. Chambers with specified minimum temperatures (such as those used in burn-in and life tests): When test requirements involve a specified minimum test temperature, the controls and chamber construction shall be such that the temperature of any point within the working area shall not deviate more than +8°C, -0°C; or +8 percent, -0 percent, whichever is greater, from the specified minimum temperature, except for the immediate vicinity of the specimens generating heat.

- 4.1.2 Electrical test frequency. Unless otherwise specified, the electrical test frequency shall be 1,000 ±25 Hertz (Hz).

- 4.1.3 Accuracy. The specified limits are for absolute (true) values, obtained with the specified (nominal) test conditions. Proper allowance shall be made for measurement errors (including those due to deviations from nominal test conditions) in establishing the working limits to be used for the measured values, so that the true values of the device parameters (as they would be under nominal test conditions) are within the specified limits.

The following electrical test tolerances and precautions, unless otherwise specified in the applicable acquisition document, shall be maintained for all device measurements to which they apply (3000, 4000 series and other specified electrical measurements). Wherever test conditions are specified in the applicable acquisition document to a precision tighter than the tolerances indicated below, the specified conditions shall apply and take precedence over these general requirements.

- a. Bias conditions shall be held to within 3 percent of the specified value.

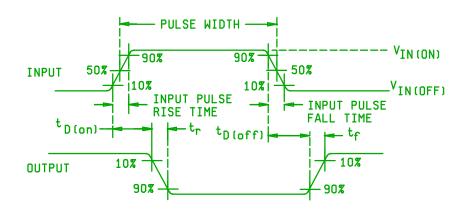

- b. Such properties as input pulse characteristics, repetition rates, and frequencies shall be held to within 10 percent. Nominal values should be chosen so that ±10 percent variation (or the actual test equipment variation, if less than 10 percent) does not affect the accuracy or validity of the measurement of the specified value.

- Voltages applied in breakdown testing shall be held within 1 percent of specified value.

- d. Resistive loads shall be  $\pm 5$  percent tolerance.

- e. Capacitive loads shall be ±10 percent or ±1 picofarad (pF) tolerance, whichever is greater.

- f. Inductive loads shall be  $\pm 10$  percent or  $\pm 5$  microhenries (mH) tolerance, whichever is greater.

- g. Static parameters shall be measured to within 1 percent.

- Switching parameters shall be measured to within 5 percent or 1 nanosecond (ns), whichever is greater.

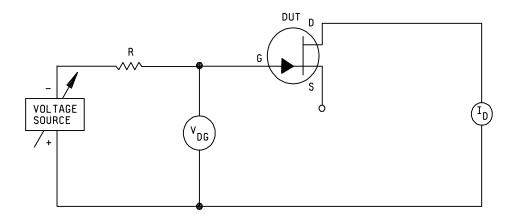

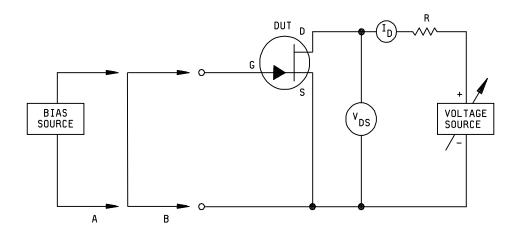

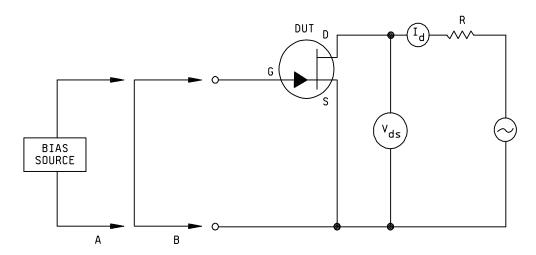

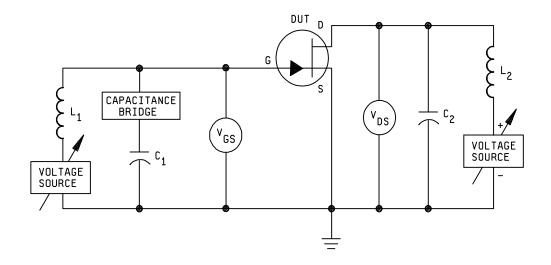

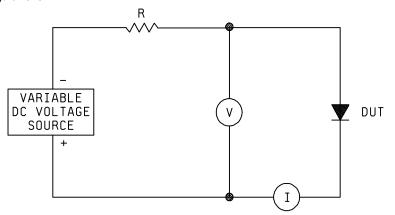

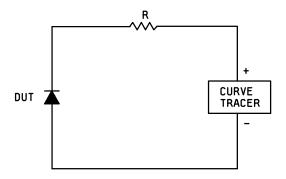

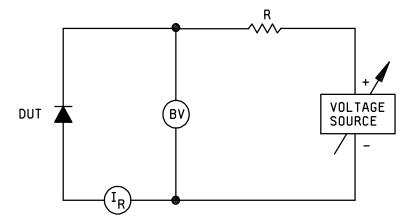

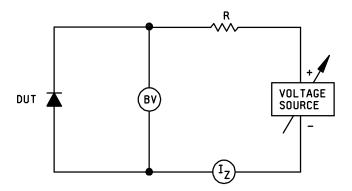

- 4.1.3.1 <u>Test methods and circuits</u>. Unless otherwise stated in the specific test method, the methods and circuits shown are given as the basic measurement method. They are not necessarily the only method or circuit which can be used, but the manufacturer shall demonstrate to the acquiring activity that alternate methods or circuits which he may desire to use are equivalent and give results within the desired accuracy of measurement (see 4.1.3).

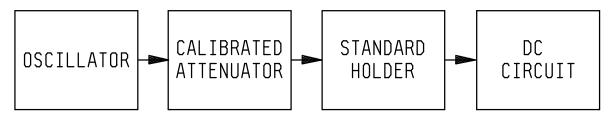

- 4.1.4 <u>Calibration requirements</u>. Calibration and certification procedures shall be provided in accordance with MIL-STD-45662 for plant standards and instruments used to measure or control production processes and semiconductor devices under test. For those measurements that are not traceable to the National Institute of Standards and Technology (NIST), correlation samples shall be maintained and used as the basis of proving acceptability when such proof is required. In addition, the following requirements shall apply:

- a. The accuracy of a calibrating instrument shall be at least four times greater than that of the item being calibrated, unless the item being calibrated is state of the art equipment, which may be near or equal in accuracy to the state of the art calibrating equipment, in which case the four time requirement does not apply. However, the instrument shall be calibrated to correlate with standards established by the NIST.

- b. Except in those cases where the NIST recommends a longer period and concurrence is obtained from the qualifying activity, calibration intervals for plant electrical standards shall not exceed one year, and for plant mechanical standards shall not exceed two years.

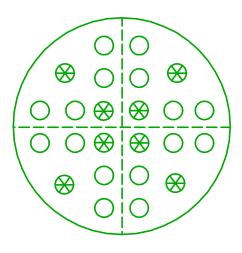

## 4.2 Orientations:

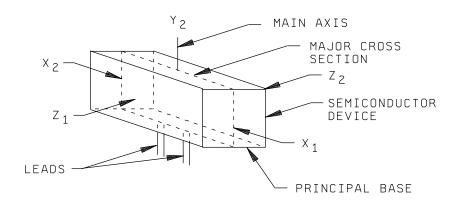

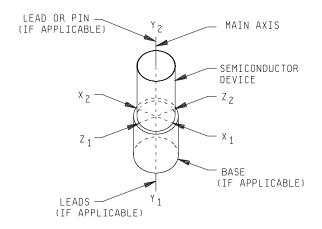

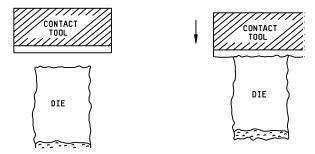

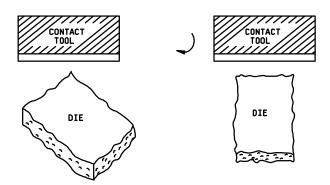

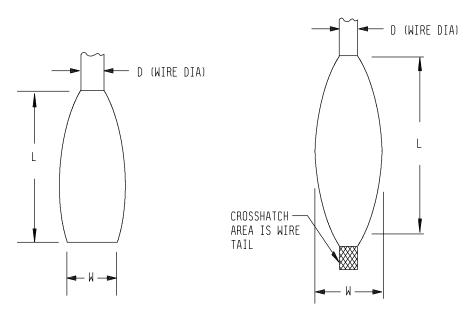

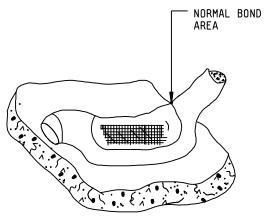

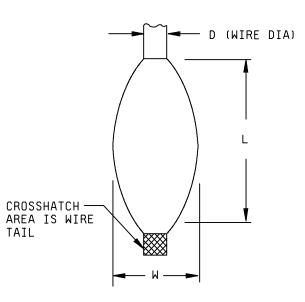

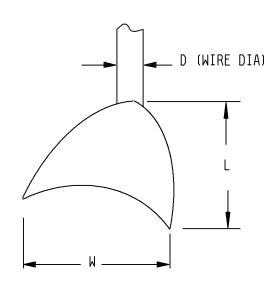

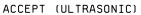

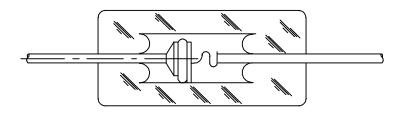

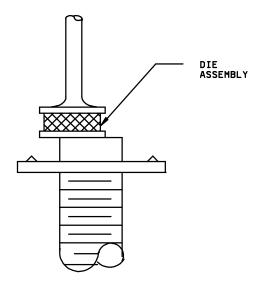

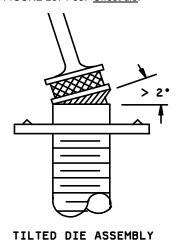

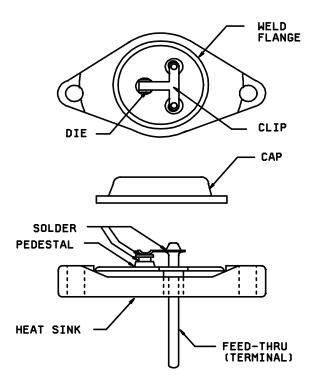

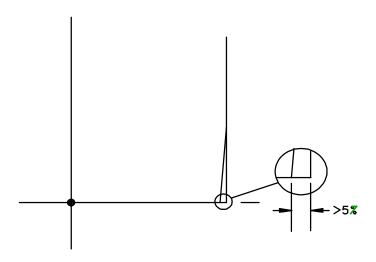

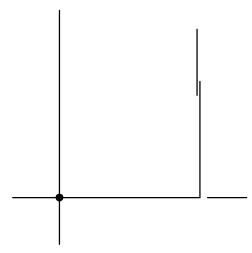

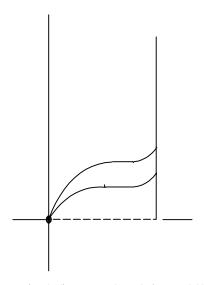

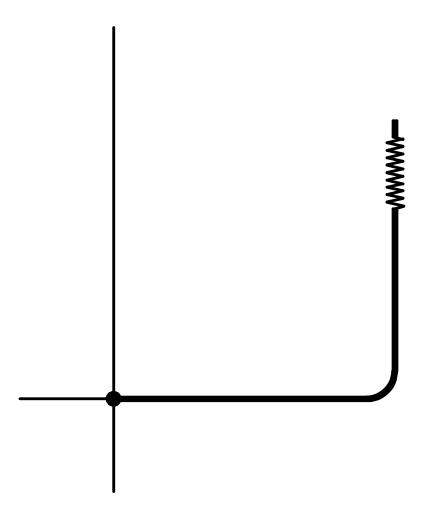

X is the orientation of a device with the main axis of the device normal to the direction of the accelerating force, and the major cross section parallel to the direction of the accelerating force.

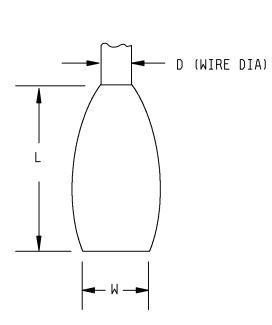

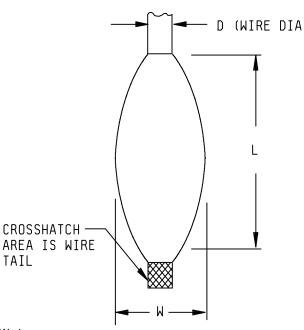

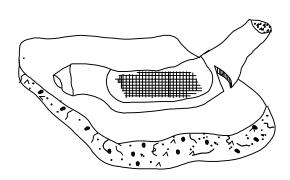

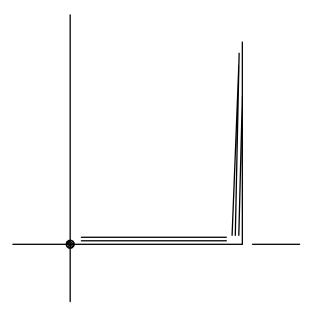

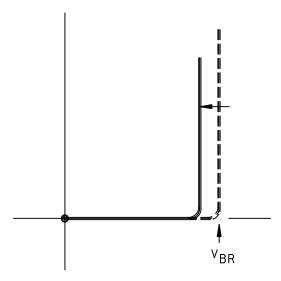

Y is the orientation of a device with the main axis of the device parallel to the direction of the accelerating force, and the principal base toward  $(Y_1)$ , or away from  $(Y_2)$ , the point of application of the accelerating force.

Z is the orientation of a device with the main axis and the major cross section of the device normal to the direction of the accelerating force. Z is 90° of X.

NOTE: For case configurations, other than those shown on figures 1 and 2, the orientation of the device shall be as specified in the individual specification.

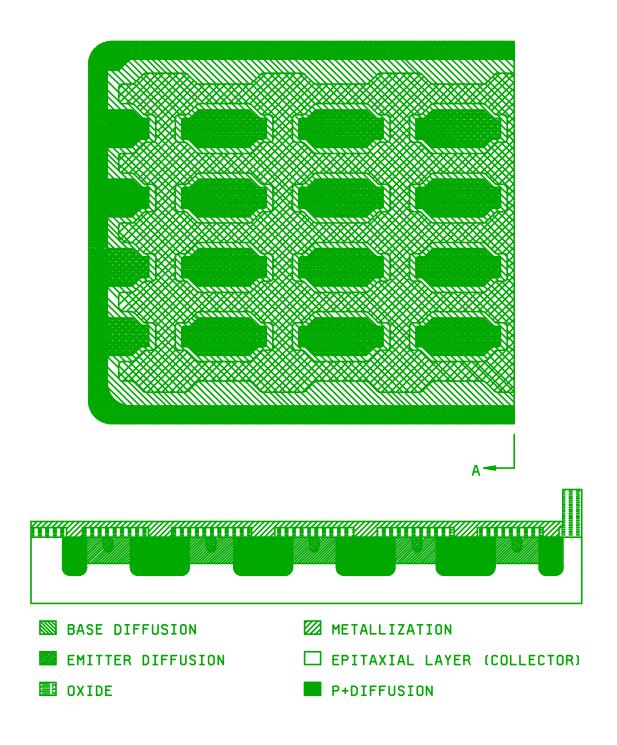

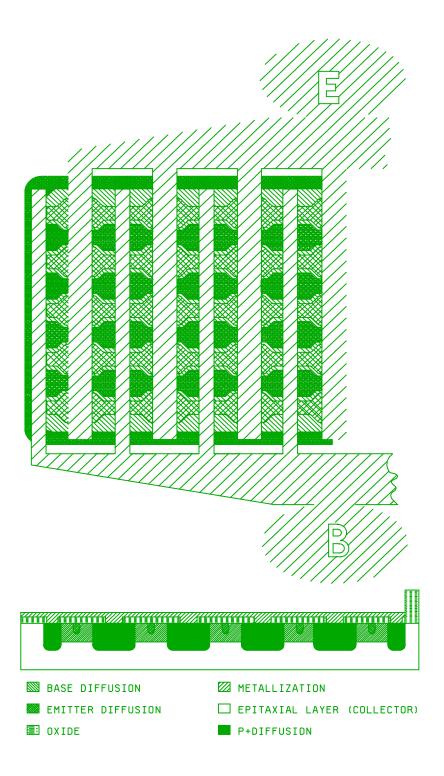

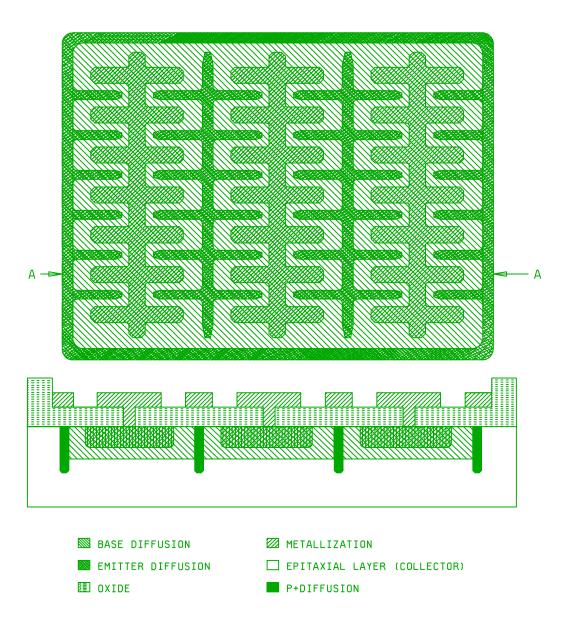

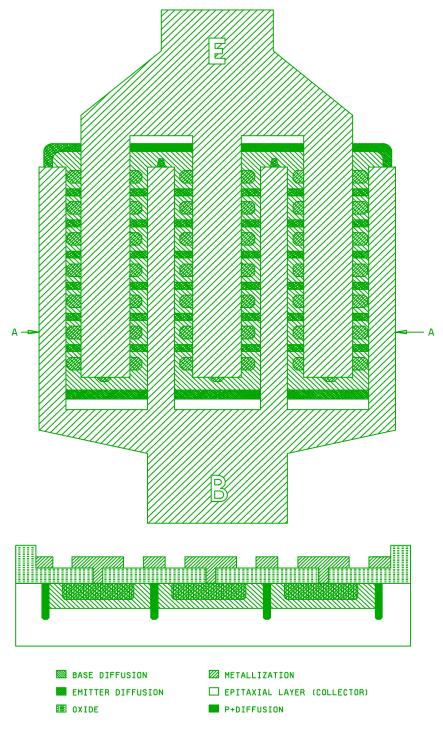

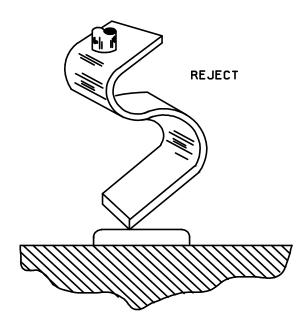

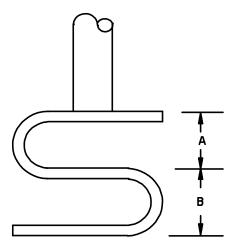

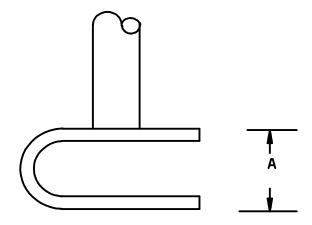

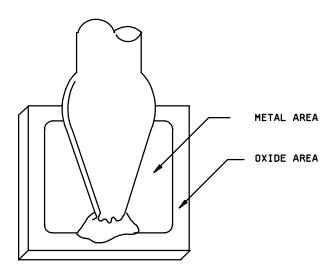

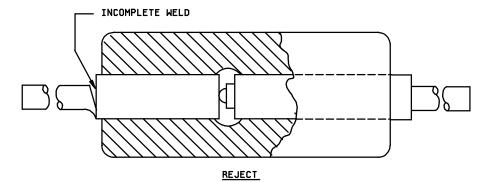

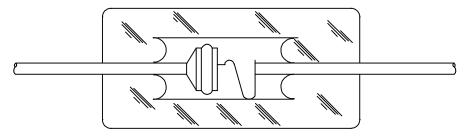

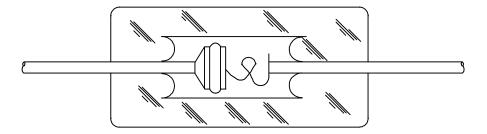

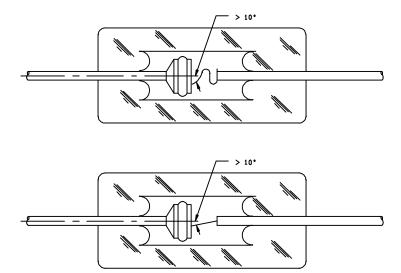

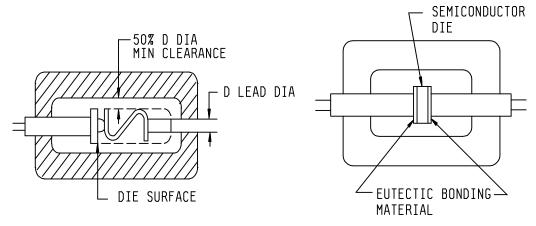

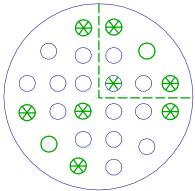

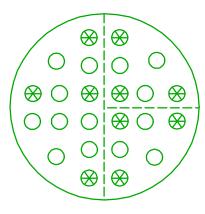

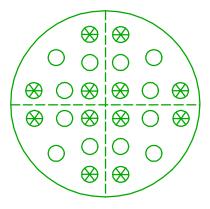

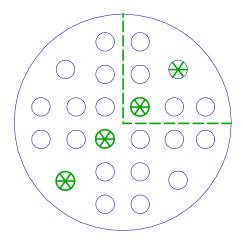

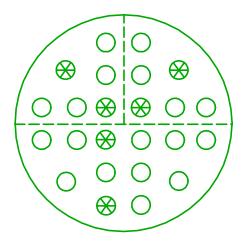

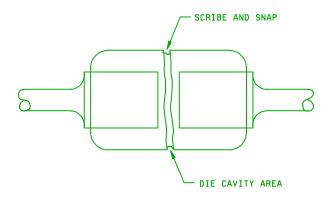

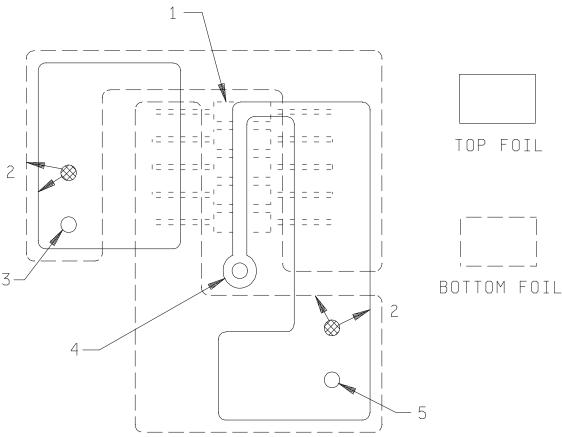

FIGURE 1. <u>Orientation of noncylindrical semiconductor</u> device to direction of accelerating force.

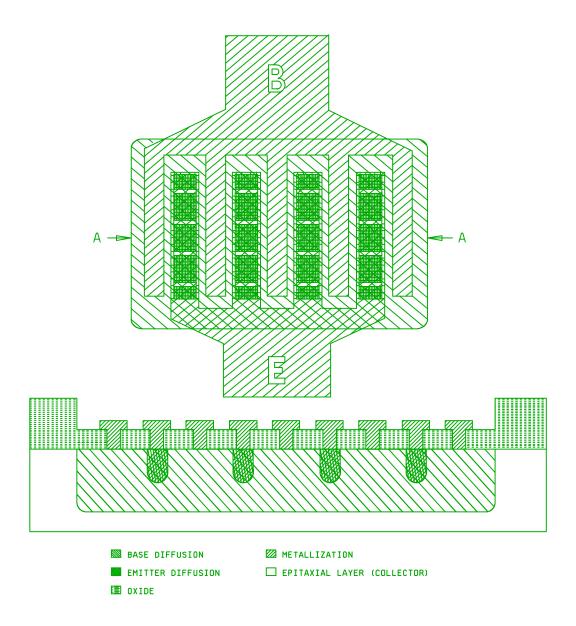

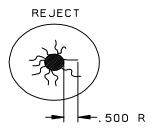

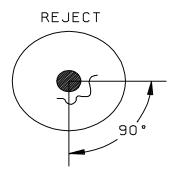

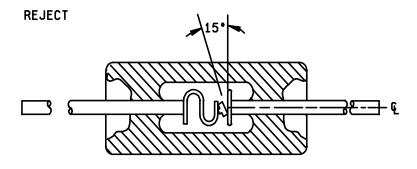

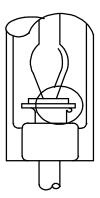

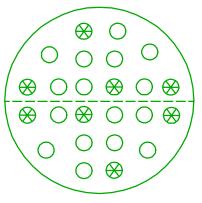

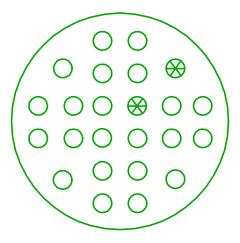

FIGURE 2. <u>Orientation of cylindrical semiconductor</u> device to direction of accelerating force.

- 4.3 General precautions. The following precautions shall be observed in testing the devices.

- 4.3.1 Transients. Devices shall not be subjected to conditions in which transients cause the rating to be exceeded.

- 4.3.2 Test conditions for electrical measurements. Unless otherwise required for a specified test method, semiconductor devices should not be subjected to any condition that will cause any maximum rating of the device to be exceeded. The precautions should include limits on maximum instantaneous currents and applied voltages. High series resistances (constant current supplies) and low capacitances are usually required. If low cutoff, or reverse current devices are to be measured, for example, nanoampere units, care should be taken to ensure that parasitic circuit currents or external leakage currents are small, compared with the cutoff or reverse current of the device to be measured.

- 4.3.2.1 <u>Steady state dc measurements (method 4000)</u>. Unless otherwise specified, all steady state dc parameters are defined using steady state dc conditions.

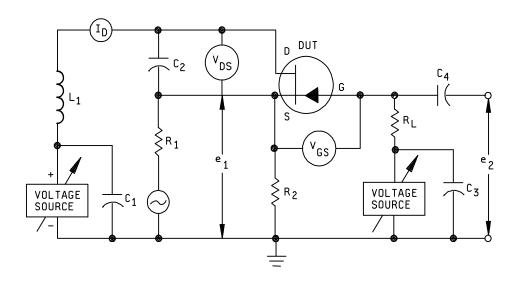

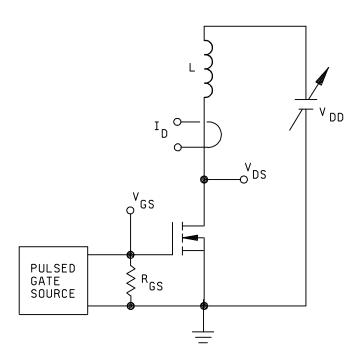

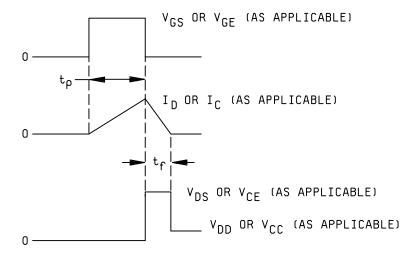

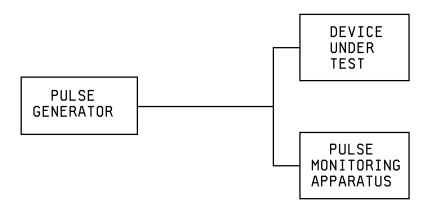

- 4.3.2.2 <u>Pulse measurements (method 4000)</u>. When device static or dynamic parameters are measured under "pulsed" conditions, in order to avoid measurement errors introduced by device heating during the measurement period, the following items should be covered in the detail specification:

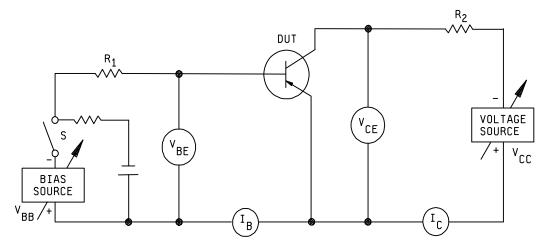

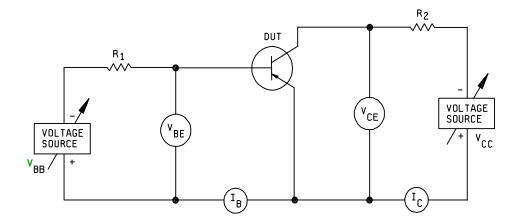

- a. The statement "Pulsed test" shall be placed by the test specified.

- b. Unless otherwise specified, the pulse time (t<sub>p</sub>) shall be ≤10 milliseconds and the duty cycle shall be a maximum of 2 percent; within this limit the pulse must be long enough to be compatible with test equipment capability and the accuracy required, and short enough to avoid heating.

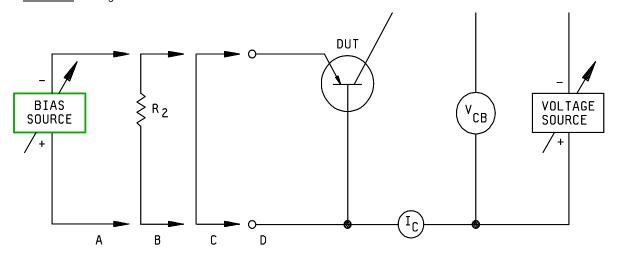

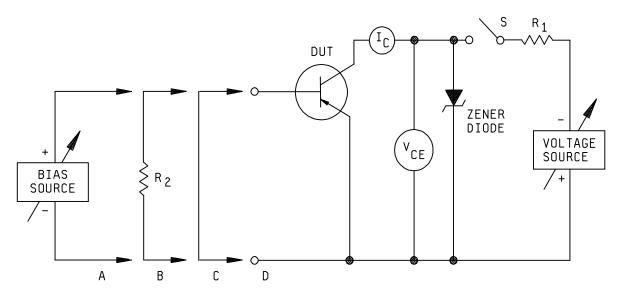

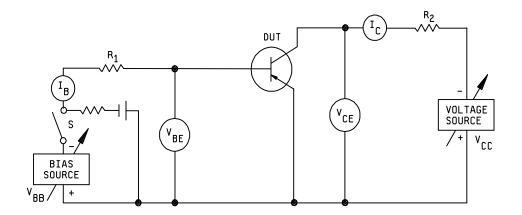

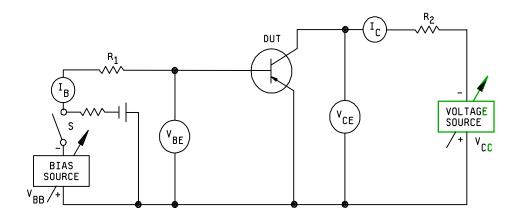

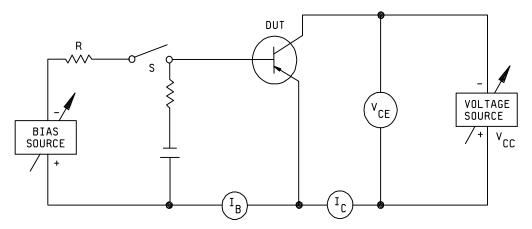

- 4.3.3 <u>Test circuits</u>. The circuits shown are given as examples which may be used for the measurements. They are not necessarily the only circuits which can be used but the manufacturer shall demonstrate to the Government that other circuits which he may desire to use will give results within the desired accuracy of measurement. Circuits are shown for PNP transistors in one circuit configuration only. They may readily be adapted for NPN devices and for other circuit configurations.

- 4.3.3.1 <u>Test method variation</u>. Variation from the specified test methods used to verify the electrical parameters are allowed provided that it is demonstrated to the preparing activity or their agent that such variations in no way relax the requirements of this specification and that they are approved before testing is performed. For proposed test variations, a test method comparative error analysis shall be made available for checking by the preparing activity or their agent.

- 4.3.4 Soldering. Adequate precautions shall be taken to avoid damage to the device during soldering required for tests.

- 4.3.5 Order of connection of leads. Care should be taken when connecting a semiconductor device to a power source. The common terminal shall be connected first.

- 4.3.6 <u>Radiation precautions</u>. Due precautions shall be used in storing or testing semiconductor devices in substantial fields of X-rays, neutrons, or other energy particles.

- 4.3.7 Handling precautions.

- 4.3.7.1 <u>UHF and microwave devices</u>. Handling precautions for UHF and microwave devices shall be as follows:

- a. Ground all equipment.

- b. Make hand contact to the equipment while holding the base end and maintain hand contact with the equipment until the device is in place.

- c. Where applicable, keep devices in metal shields until they are inserted in the equipment or until necessary to remove for test.

- 4.3.7.2 <u>Electrostatic discharge sensitive devices</u>. Handling precautions shall be observed in accordance with DOD-HDBK-263 during testing of Electrostatic Discharge Sensitive (ESDS) devices. The area where ESDS device tests are performed shall meet the requirements of an ESD Protected Area of MIL-STD-1686.

- 4.4 <u>Continuity verification of burn-in and life tests</u>. The test setup shall be monitored at the test temperature initially and at the conclusion of the test to establish that all devices are being stressed to the specified requirements. The following is the minimum acceptable monitoring procedure:

- a. Device sockets. Initially and at least each 6 months thereafter, each test board or tray shall be checked to verify continuity to connector points to assure that the correct voltage bias will be applied. Except for this initial and periodic verification, each device or device socket does not have to be checked; however, random sampling techniques shall be applied prior to each time a board is used and shall be adequate to assure that there are correct and continuous electrical connections to the DUTs.

- b. Connectors to test boards or trays. After the test boards are loaded with devices, inserted into the system, and brought up to the specified operating conditions, each required test voltage and signal condition shall be verified in at least one location on each test board or tray so as to assure electrical continuity and the correct application of specified electrical stresses for each connection or contact pair used in the applicable test configuration. The system may be opened for a maximum of 10 minutes.

- c. At the conclusion of the test period, prior to removal of devices from temperature and bias conditions, the voltage and signal condition verification of 4.4b shall be repeated.

- d. For class S devices, each test board or tray and each test socket shall be verified prior to test to assure that the specified bias conditions are applied to each device. This may be accomplished by verifying the device functional response at each device output(s) or by performing a socket verification on each socket prior to loading. An approved alternate procedure may be used.

- 4.4.1 <u>Bias interruption</u>. Where failures or open contacts occur which result in removal of the required bias stresses for any period of the required bias duration, the bias time shall be extended to assure actual exposure for the total minimum specified test duration. Any loss(es) or interruption(s) of bias in excess of 10 minutes total duration while the chamber is at temperature during the final 8 hours of burn-in shall require extension of the bias duration for an uninterrupted 8 hours minimum, after the last bias interruption.

### 4.5 Requirements for HTRB and burn-in.

- a. The temperature of +20°C minimum is the ambient air temperature to which all devices should be exposed during power screening where room ambient is specified.

- b. An increase in effective ambient temperature from cumulative induced power to DUTs shall not result in device junction temperature exceeding maximum ratings.

- c. Ambient temperature shall not be measured in the convection current (above) or downstream (Fan Air) of DUTs.

- d. Moving air greater than 30 CFM (natural convection) may be allowed for the purpose of temperature equalization within high device density burn-in racks.

- e. High velocity or cooled air shall not be used for the purpose of increasing device ratings.

- f. Power up of burn-in racks may occur when ambient is less than specified. When thermal equilibrium has been reached, or five hours maximum has occurred, the ambient shall be at the specified value. Time accrued prior to reaching specified ambient shall not be chargeable, to the life test duration.

- g. If the ambient at or beyond the five hour point is not the specified value, a nonconformance shall exist requiring corrective action.

- h. Time is not chargeable during the period when specified conditions are not maintained. If device maximum ratings(if life test, finish the test and use for credit; if shippable, use this criteria)are exceeded and the manufacturer intends to submit the lot affected, the product on test must be evaluated by re-starting the burn-in or HTRB from zero hours at the specified temperature and verifying that the end-point failure rate is typical for this product type from a review of established records.

- i. Chamber temperature for HTRB and burn-in shall be controlled to ±3 percent of the specified value. (Unless otherwise specified in 4.1.1.) This temperature shall be maintained within the chamber. Forced air may be used to equalize temperature within the chamber but shall not be used as a coolant to increase device power capability.

# 4.6 Bias requirements.

a. Bias errors at the power supply source caused by changing power supply loads during temperature transitions shall not exceed ±5 percent of that specified value.

SUPERSEDES PAGE 9 OF MIL-STD-750D

- b. Bias values at the source, during stabilized conditions, shall not exceed ±3 percent of the specified value.

- c. Burn-in apparatus shall be arranged so as to result in the approximate average power dissipation for each device whether devices are tested individually or in a group. Bias and burn-in circuitry tolerances should not vary test conditions to individual devices by more than ±5 percent of specified conditions.

- d. Normal variation in individual device characteristics need not be compensated for by burn-in circuitry.

- e. Burn-in equipment shall be arranged so that the existence of failed or abnormal devices in a group does not negate the effect of the test for other devices in the group. Periodic verification will assure that specified conditions are being maintained. Verification shall be performed, as a minimum, at the starting and end of screening.

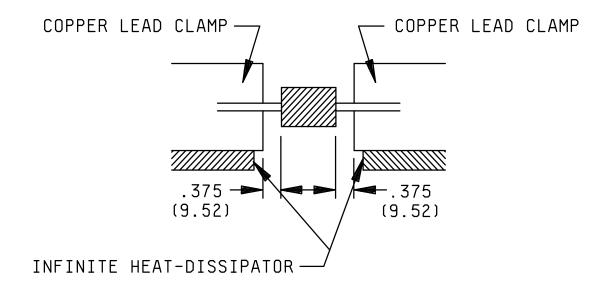

- f. Lead, stud, or case mounted devices shall be mounted in their normal mounting configuration and the point of mechanical connection shall be maintained at no less than the specified ambient.

- 4.7 <u>Destructive tests</u>. Unless otherwise demonstrated, the following MIL-STD-750 tests are classified as destructive:

| METHOD NUMBER         | TEST                                      |

|-----------------------|-------------------------------------------|

| 1017                  | Neutron irradiation                       |

| 1019                  | Steady state total dose irradiation       |

| 1020                  | ESDS classification                       |

| 1021                  | Moisture resistance                       |

| 1036,1037             | Intermittent operation life               |

| 1041                  | Salt atmosphere                           |

| 1042<br>(Condition D) | Burn-in/life test for power MOSFETs       |

| 1046                  | Salt spray                                |

| 1056                  | Thermal shock (glass strain)              |

| 2017                  | Die shear test                            |

| 2031                  | Soldering heat                            |

| 2036                  | Terminal strength                         |

| 2037                  | Post seal bond strength                   |

| 2075                  | Decap internal visual design verification |

| 2077                  | SEM                                       |

All other mechanical or environmental tests (other than those listed in 4.8) shall be considered destructive initially, but may subsequently be considered nondestructive upon accumulation of sufficient data to indicate that the test is nondestructive. The accumulation of data from five repetitions of the specified test on the same sample of product, without significant evidence of cumulative degradation in any device in the sample, is considered sufficient evidence that the test is nondestructive for the device of that manufacturer. Any test specified as a 100 percent screen shall be considered nondestructive for the stress level and duration or number of cycles applied as a screen.

SUPERSEDES PAGE 10 OF MIL-STD-750D

4.8 Nondestructive tests. Unless otherwise demonstrated, the following MIL-STD-750 tests are classified as nondestructive:

| Mathadassalas                                     | T                                                                                                                        |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Method number                                     | Test                                                                                                                     |

| 1001                                              | Barometric pressure                                                                                                      |

| 1022                                              | Resistance to solvents                                                                                                   |

| 1026, 1027                                        | Steady-state life                                                                                                        |

| 1031, 1032                                        | High temperature life (non-operating)                                                                                    |

| 1038, 1039, 1040                                  | Burn-in screen                                                                                                           |

| 1042 (Condition A, B, and C)                      | Burn-n/life test for power MOSFETs                                                                                       |

| 1051 (100 cycles or less)                         | Thermal shock (temperature cycling)                                                                                      |

| 1071                                              | Hermetic seal tests                                                                                                      |

| 2006                                              | Constant acceleration                                                                                                    |

| 2016                                              | Shock                                                                                                                    |

| 2026                                              | Solderability (if the original lead finish is unchanged and if the maximum allowable number of reworks is not exceeded.) |

| 2052                                              | PIND test                                                                                                                |

| 2056                                              | Vibration, variable frequency                                                                                            |

| 2066                                              | Physical dimensions                                                                                                      |

| 2069, 2070, 2072, 2073, 2074                      | Internal visual (pre-cap)                                                                                                |

| 2071                                              | External visual                                                                                                          |

| 2076                                              | Radiographic inspection                                                                                                  |

| 2081                                              | Forward instability shock test (FIST)                                                                                    |

| 2082                                              | Backward instability shock test (BIST)                                                                                   |

| 3101                                              | Thermal impedance testing of diodes                                                                                      |

| 3103                                              | Thermal impedance measurements for IGBTs                                                                                 |

| 3104                                              | Thermal impedance measurements for GaAs                                                                                  |

| 3051, 3052, 3053<br>(with limited supply voltage) | Safe operating area (SOA) (condition A for method 3053)                                                                  |

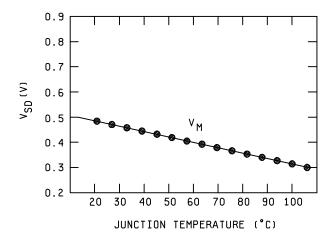

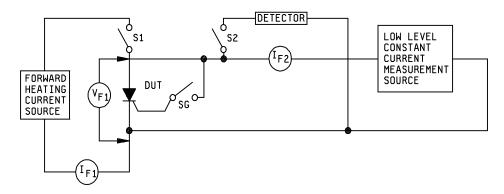

| 3131                                              | Thermal resistance (emitter to base forward voltage, emitter-only switching method)                                      |

| 4066                                              | Surge current                                                                                                            |

| 4081                                              | Thermal resistance of lead mounted diode (forward voltage, switching method)                                             |

When the junction temperature exceeds the device maximum rated junction temperature for any operation or test (including electrical stress test), these tests shall be considered destructive except under transient surge or nonrepetitive fault conditions or approved accelerated screening when, it may be desirable to allow the junction temperature to exceed the rated junction temperature. The feasibility shall be determined on a part by part basis and in the case where it is allowed adequate sample testing shall be performed to provide the proper reliability safeguards.

4.9 <u>Laboratory suitability</u>. Prior to processing any semiconductor devices intended for use in any military system or subsystem, the facility performing the test(s) must be audited by the Defense Electronics Supply Center, Sourcing and Qualification Division (DESC-ELST) and be granted written Laboratory Suitability status for each test method to be employed. Processing of any devices by any facility without Laboratory Suitability status for the test methods used shall render the processed devices nonconforming.

# 5. DETAILED REQUIREMENTS (NOT APPLICABLE)

## 6. NOTES

6.1 <u>International standardization agreement</u>. Certain provisions of this standard are the subject of international standardization agreement. When amendment, revision, or cancellation of this standard is proposed which will affect or violate the international agreement concerned, the preparing activity will take appropriate reconciliation action through international standardization channels, including departmental standardization offices, if required.

Custodians:

Navy - EC Army - ER Air Force - 17 NASA - NA

Review activities: Army - AR, ER, MI

Navy - AS, CG, MC, SH Air Force - 19, 85, 99 Preparing activity: DLA - EC

(Project 5961-1451)

SUPERSEDES PAGE 12 OF MIL-STD-750D

NUMERICAL INDEX

of

TEST METHODS

# Numerical index of test methods

| Method no.                                                                                                                                                                                                                                                                             | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                        | Environmental tests (1000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1001.2<br>1011.1<br>1015.1<br>1016.1<br>1017.1<br>1018<br>1019.4<br>1020.2<br>1021.3<br>1022.5<br>1026.5<br>1027.3<br>1031.5<br>1032.2<br>1036.3<br>1037.2<br>1038.4<br>1039.4<br>1040<br>1041.3<br>1046.3<br>1048<br>1049<br>1051.5<br>1055.1<br>1055.1<br>1066.1<br>1066.1<br>1071.6 | Barometric pressure (reduced). Immersion. Steady-state primary photocurrent irradiation procedure (electron beam). Insulation resistance. Neutron irradiation. Internal water-vapor content. Steady-state total dose irradiation procedure. Electrostatic discharge sensitivity (ESDS) classification. Moisture resistance. Resistance to solvents. Steady-state operation life. Steady-state operation life (sample plan). High-temperature life (nonoperating). High-temperature (nonoperating) life (sample plan). Intermittent operation life. Intermittent operation life. Intermittent operation life (sample plan). Burn-in (for diodes, rectifiers, and zeners). Burn-in (for transistors). Burn-in (for thyristors (controlled rectifiers)). Salt atmosphere (corrosion). Burn-in and life test for power MOSFET's or insulated gate bipolar transistors (IGBT). Salt spray (corrosion). Blocking life. Blocking life (sample plan). Temperature cycling (air to air). Potted environment stress test. Monitored mission temperature cycle. Thermal shock (liquid to liquid). Temperature measurement, case and stud. Dew point. Hermetic seal. |

|                                                                                                                                                                                                                                                                                        | Mechanical characteristics tests (2000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2005.2<br>2006<br>2016.2<br>2017.2<br>2026.10<br>2031.2<br>2036.4<br>2037<br>2046.1<br>2051.1<br>2052.2<br>2056<br>2057.1<br>2066<br>2068<br>2069.1<br>2070.1<br>2071.3<br>2072.6<br>2073<br>2074.4<br>2075                                                                            | Axial lead tensile test. Constant acceleration. Shock. Die attach integrity. Solderability. Soldering heat. Terminal strength. Bond strength. Vibration fatigue. Vibration noise. Particle impact noise detection (PIND) test. Vibration, variable frequency. Vibration, variable frequency (monitored). Physical dimensions. External visual for nontransparent, glass-encased, double plug, noncavity, axial leaded diodes. Pre-cap visual, power MOSFET's. Pre-cap visual microwave discrete and multichip transistors. Visual and mechanical examination. Internal visual transistor (pre-cap) inspection. Visual inspection for die (semiconductor diode). Internal visual design verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Method no.                                                                                                                                               | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                          | Mechanical characteristics tests (2000 series) - Continued.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2076.3<br>2077.3<br>2081<br>2082<br>2101<br>2102                                                                                                         | Radiography. Scanning electron microscope (SEM) inspection of metallization. Forward instability, shock (FIST). Backward instability, vibration (BIST). DPA procedures for diodes. DPA procedures for wire bonded devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                          | Electrical characteristics tests for bipolar transistors (3000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3001.1<br>3005.1<br>3011.2<br>3015<br>3020<br>3026.1<br>3030<br>3036.1<br>3041.1<br>3051<br>3052<br>3053<br>3061.1<br>3066.1<br>3071<br>3076.1<br>3086.1 | Breakdown voltage, collector to base. Burnout by pulsing. Breakdown voltage, collector to emitter. Drift. Floating potential. Breakdown voltage, emitter to base. Collector to emitter voltage. Collector to base cutoff current. Collector to emitter cutoff current. Safe operating area (continuous dc). Safe operating area (pulsed). Safe operating area (switching). Emitter to base cutoff current. Base emitter voltage (saturated or nonsaturated). Saturation voltage and resistance. Forward-current transfer ratio. Static input resistance.                                                                                                                                                                                                                                                                                                                               |

| 3092.1                                                                                                                                                   | Static transconductance.  Circuit performance and thermal resistance measurements (2100 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

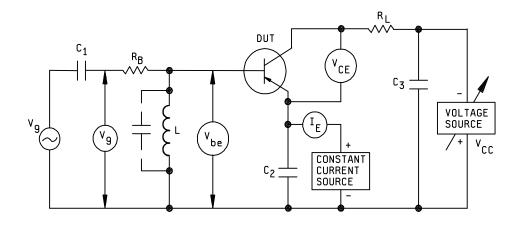

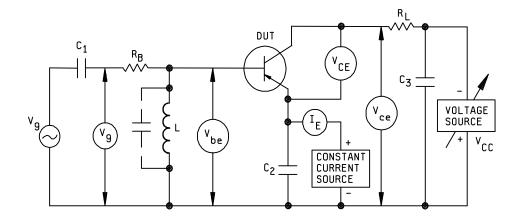

| 3101.3<br>3103<br>3104<br>3105.1<br>3126<br>3131.2<br>3132<br>3136<br>3141<br>3146.1<br>3151<br>3161<br>3181                                             | Circuit-performance and thermal resistance measurements (3100 series).  Thermal impedance testing of diodes. Thermal impedance measurements for insulated gate bipolar transistor (delta gate-emitter on voltage method). Thermal impedance measurements of GaAs MOSFET's (constant current forward-biased gate voltage method). Measurement method for thermal resistance of a bridge rectifier assembly. Thermal resistance (collector-cutoff-current method). Thermal impedance measurements for bipolar transistors (delta base-emitter voltage method). Thermal resistance (dc forward voltage drop, emitter base, continuous method). Thermal response time. Thermal response time. Thermal resistance, general. Thermal resistance, general. Thermal impedance measurements for vertical power MOSFET's (delta source-drain voltage method). Thermal resistance for thyristors. |

|                                                                                                                                                          | Low frequency tests (3200 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3201.1<br>3206.1<br>3211<br>3216<br>3221<br>3231<br>3236<br>3240.1<br>3241                                                                               | Small-signal short-circuit input impedance. Small-signal short-circuit forward-current transfer ratio. Small-signal open-circuit reverse-voltage transfer ratio. Small-signal open-circuit output admittance. Small-signal short-circuit input admittance. Small-signal short-circuit output admittance. Open circuit output capacitance. Input capacitance (output open-circuited or short-circuited). Direct interterminal capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                      | Transficating of too mornous Continuous.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Method no.                                                                                                                                                                                           | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                      | Low frequency tests (3200 series) - Continued.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3246.1<br>3251.1<br>3255<br>3256<br>3261.1<br>3266                                                                                                                                                   | Noise figure. Pulse response. Large signal power gain. Small signal power gain. Extrapolated unity gain frequency. Real part of small-signal short circuit input impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                      | High frequency tests (3300 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3301<br>3306.3<br>3311<br>3320                                                                                                                                                                       | Small-signal short-circuit forward-current transfer-ratio cutoff frequency. Small-signal short-circuit forward-current transfer ratio. Maximum frequency of oscillation. RF power output, RF power gain, and collector efficiency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                      | Electrical characteristics tests for MOS field-effect transistors (3400 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3401.1<br>3403.1<br>3404<br>3405.1<br>3407.1<br>3411.1<br>3413.1<br>3415.1<br>3421.1<br>3423<br>3431<br>3433<br>3453<br>3455<br>3457<br>3459<br>3461<br>3469<br>3470.2<br>3471.1<br>3472.2<br>3473.1 | Breakdown voltage, gate to source. Gate to source voltage or current.  MOSFET threshold voltage. Drain to source on-state voltage. Breakdown voltage, drain to source. Gate reverse current. Drain current. Drain current. Drain reverse current. Static drain to source on-state resistance. Small-signal, drain to source on state resistance. Small-signal, common-source, short-circuit, input capacitance. Small-signal, common-source, short-circuit, reverse-transfer capacitance. Small-signal, common-source, short-circuit, output admittance. Small-signal, common-source, short-circuit, forward transadmittance. Small-signal, common-source, short-circuit, reverse transfer admittance. Pulse response (FET). Small-signal, common-source, short-circuit, input admittance. Repetitive unclamped inductive switching. Single pulse unclamped inductive switching. Gate charge. Switching time test. Reverse recovery time (trr) and recovered charge (Qrr) for power MOSFET (drain-to-source) and power rectifiers |

| 3474.1<br>3475.1<br>3476<br>3477.1<br>3478.1<br>3479<br>3490                                                                                                                                         | with $t_{rr} \le 100$ ns.  Safe operating area for power MOSFET's or insulated gate bipolar transistors.  Forward transconductance (pulsed dc method) of power MOSFET's or insulated gate bipolar transistors.  Commutating diode for safe operating area test procedure for measuring dv/dt during reverse recovery of power MOSFET transistors or insulated gate bipolar transistors.  Measurement of insulated gate bipolar transistor total switching losses and switching times.  Power transistor electrical dose rate test method.  Short circuit withstand time.  Clamped inductive switching safe operating area for MOS gated power transistors.                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                      | Electrical characteristics tests for Gallium Arsenide transistors (3500 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3501<br>3505<br>3510<br>3570<br>3575                                                                                                                                                                 | Breakdown voltage, drain to source.  Maximum available gain of a GaAs FET.  1 dB compression point of a GaAs FET.  GaAs FET forward gain (Mag S21).  Forward transconductance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Method no.                                                                                                                                                                           | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

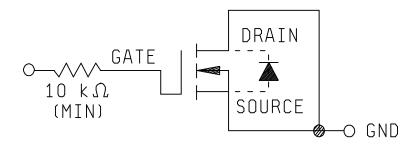

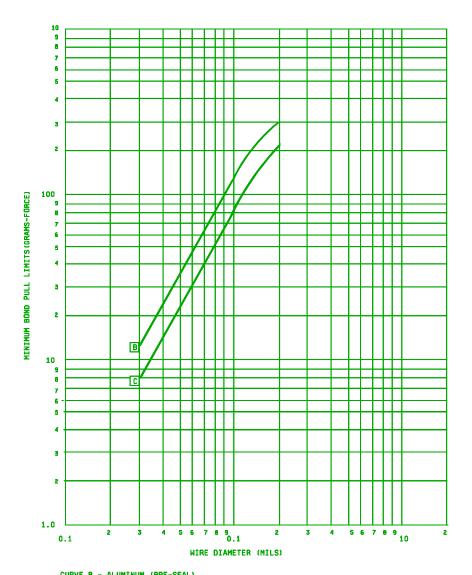

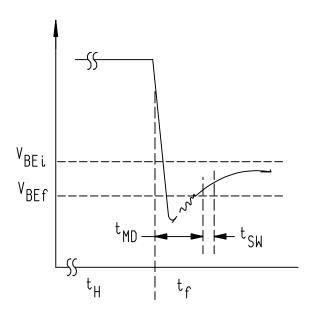

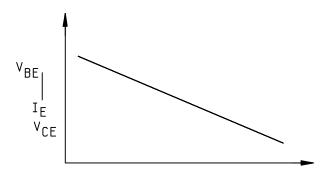

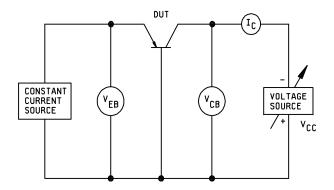

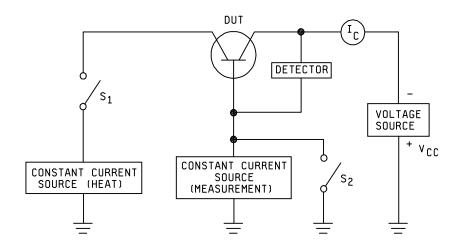

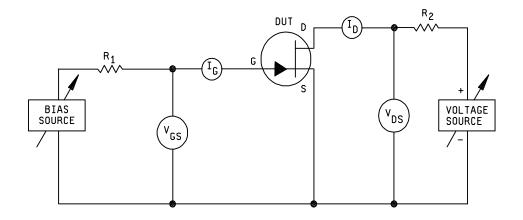

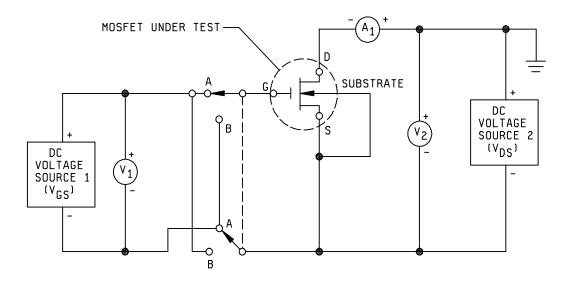

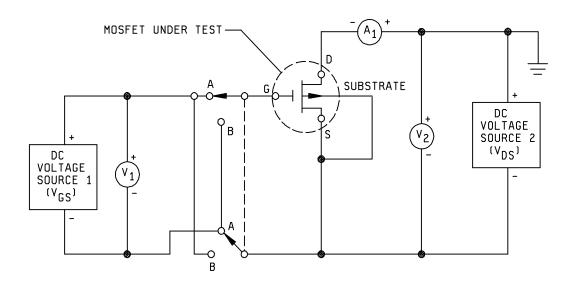

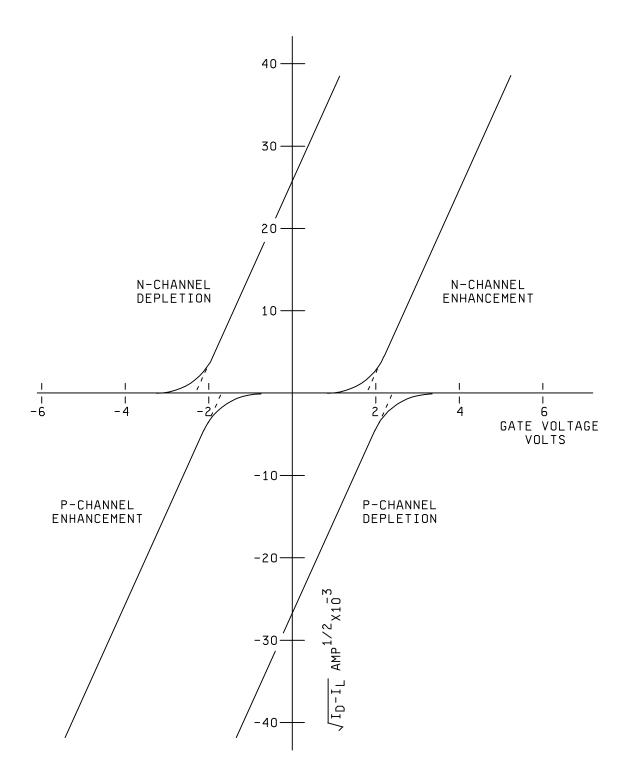

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|